- 您現在的位置:買賣IC網 > PDF目錄384755 > MT48LC4M32B2 (Micron Technology, Inc.) SYNCHRONOUS DRAM PDF資料下載

參數資料

| 型號: | MT48LC4M32B2 |

| 廠商: | Micron Technology, Inc. |

| 英文描述: | SYNCHRONOUS DRAM |

| 中文描述: | 同步DRAM |

| 文件頁數: | 22/52頁 |

| 文件大小: | 1281K |

| 代理商: | MT48LC4M32B2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

22

128Mb: x32 SDRAM

128MbSDRAMx32_D.p65 – Rev. D; Pub. 6/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2002, Micron Technology, Inc.

128Mb: x32

SDRAM

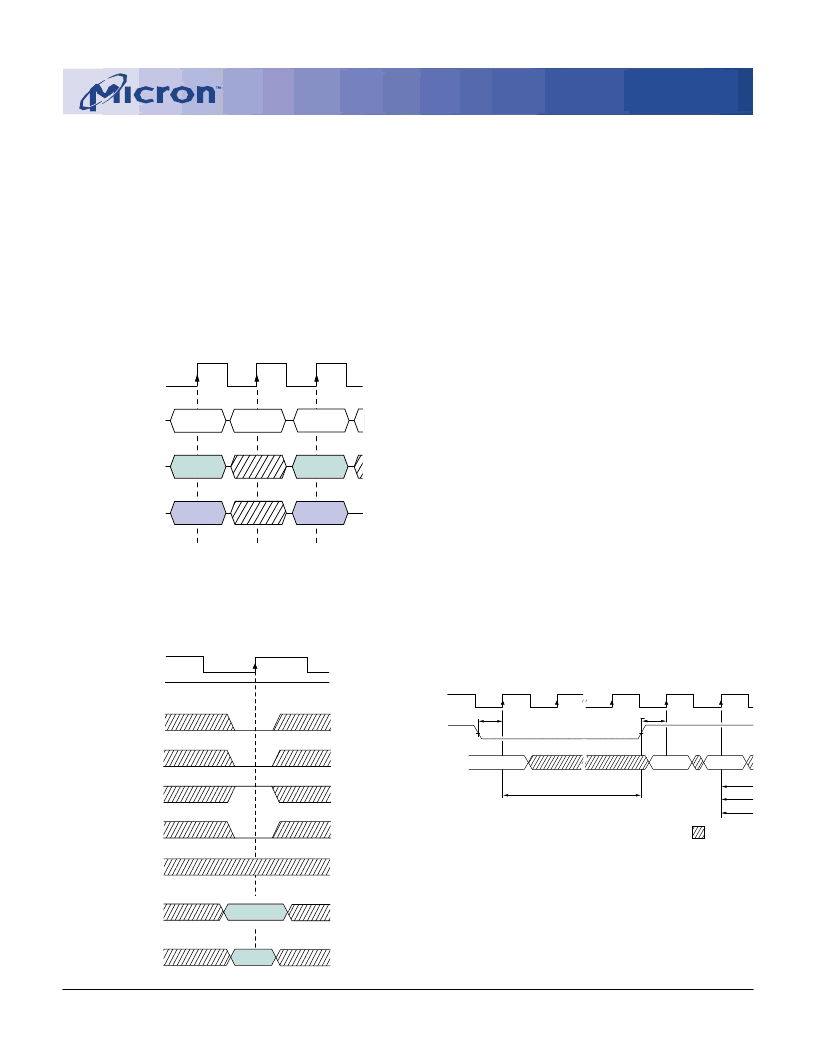

Fixed-length or full-page WRITE bursts can be trun-

cated with the BURST TERMINATE command. When

truncating a WRITE burst, the input data applied coin-

cident with the BURST TERMINATE command will be

ignored. The last data written (provided that DQM is

LOW at that time) will be the input data applied one

clock previous to the BURST TERMINATE command.

This is shown in Figure 19, where data

n

is the last

desired data element of a longer burst.

Figure 21

Power-Down

DON’T CARE

tRAS

tRC

tRCD

All banks idle

Input buffers gated off

Exit power-down mode.

(

)

(

)

(

)

(

)

(

)

(

)

tCKS

> tCKS

COMMAND

NOP

ACTIVE

Enter power-down mode.

NOP

CLK

CKE

(

)

(

)

(

)

(

)

Figure 20

PRECHARGE Command

Figure 19

Terminating a WRITE Burst

CLK

DQ

T2

T1

T0

COMMAND

ADDRESS

BANK,

COL

n

WRITE

BURST

TERMINATE

NEXT

COMMAND

D

IN

n

(ADDRESS)

(DATA)

NOTE:

DQMs are LOW.

PRECHARGE

The PRECHARGE command (Figure 20) is used to

deactivate the open row in a particular bank or the

open row in all banks. The bank(s) will be available for

a subsequent row access some specified time (

t

RP) af-

ter the PRECHARGE command is issued. Input A10

determines whether one or all banks are to be

precharged, and in the case where only one bank is to

be precharged, inputs BA0 and BA1 select the bank.

When all banks are to be precharged, inputs BA0 and

BA1 are treated as “Don’t Care.” Once a bank has been

precharged, it is in the idle state and must be activated

prior to any READ or WRITE commands being issued to

that bank.

POWER-DOWN

Power-down occurs if CKE is registered LOW coinci-

dent with a NOP or COMMAND INHIBIT when no ac-

cesses are in progress (see Figure 21). If power-down

occurs when all banks are idle, this mode is referred to

as precharge power-down; if power-down occurs when

there is a row active in either bank, this mode is referred

to as active power-down. Entering power-down deacti-

vates the input and output buffers, excluding CKE, for

maximum power savings while in standby. The device

may not remain in the power-down state longer than

the refresh period (64ms) since no refresh operations

are performed in this mode.

The power-down state is exited by registering a NOP

or COMMAND INHIBIT and CKE HIGH at the desired

clock edge (meeting

t

CKS).

CS#

WE#

CAS#

RAS#

CKE

CLK

A10

HIGH

All Banks

Bank Selected

A0-A9, A11

BA0,1

ABANK

相關PDF資料 |

PDF描述 |

|---|---|

| MT48LC4M32LFFC | SYNCHRONOUS DRAM |

| MT48LC64M8A2 | SYNCHRONOUS DRAM |

| MT48LC32M16A2 | SYNCHRONOUS DRAM |

| MT48LC8M16A2FB-75LIT | SYNCHRONOUS DRAM |

| MT48LC8M16A2FB-7E | SYNCHRONOUS DRAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MT48LC4M32B27 | 制造商:MT 功能描述:NEW |

發(fā)布緊急采購,3分鐘左右您將得到回復。