- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371134 > MPC604E (Motorola, Inc.) PowerPC 604e-TM RISC Microprocessor Technical Summary PDF資料下載

參數(shù)資料

| 型號: | MPC604E |

| 廠商: | Motorola, Inc. |

| 英文描述: | PowerPC 604e-TM RISC Microprocessor Technical Summary |

| 中文描述: | 的PowerPC 604e -商標RISC微處理器技術總結 |

| 文件頁數(shù): | 15/34頁 |

| 文件大小: | 117K |

| 代理商: | MPC604E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

PowerPC 604e RISC Microprocessor Technical Summary

15

1.2.11 System Interface/Bus Interface Unit (BIU)

The 604e provides a versatile bus interface that allows a wide variety of system design options. The

interface includes a 72-bit data bus (64 bits of data and 8 bits of parity), a 36-bit address bus (32 bits of

address and 4 bits of parity), and sufficient control signals to allow for a variety of system-level

optimizations. The 604e uses one-beat and four-beat data transactions, although it is possible for other bus

participants to perform longer data transfers. The 604e clocking structure supports processor-to-bus clock

ratios of 1:1, 3:2, 2:1, 5:2, 3:1, and 4:1, as described in Section 1.2.12, “Clocking.” Note that support for

processor/bus clock ratios 5:2 and 4:1 is specific to the 604e and is not supported in the 604.

To support the changes in the clocking configuration, different precharge timings for the ABB, DBB,

ARTRY, and SHD signals are implemented internally by the processor. The precharge timings for ARTRY

and SHD can be disabled by setting HID0[7].

The 604e has the same pin configuration as the 604; however, on the 604e Vdd and AVdd must be tied to

2.5 Vdc and OVdd must be tied to 3.3 Vdc. The 604e uses split voltage planes, and for replacement

compatibility, 604/604e designs should provide both 2.5-V and 3.3-V planes and the ability to tie those two

planes together and disable the 2.5-V plane for operation with a 604.

In addition to the normal and data-streaming modes implemented on the 604, a no-DRTRY mode is

implemented on the 604e that improves performance on read operations for systems that do not use the

DRTRY signal. No-DRTRY mode makes read data available to the processor one bus clock cycle sooner

than in normal mode

.

In no-DRTRY mode, the DRTRY signal is no longer sampled as part of a qualified

bus grant.

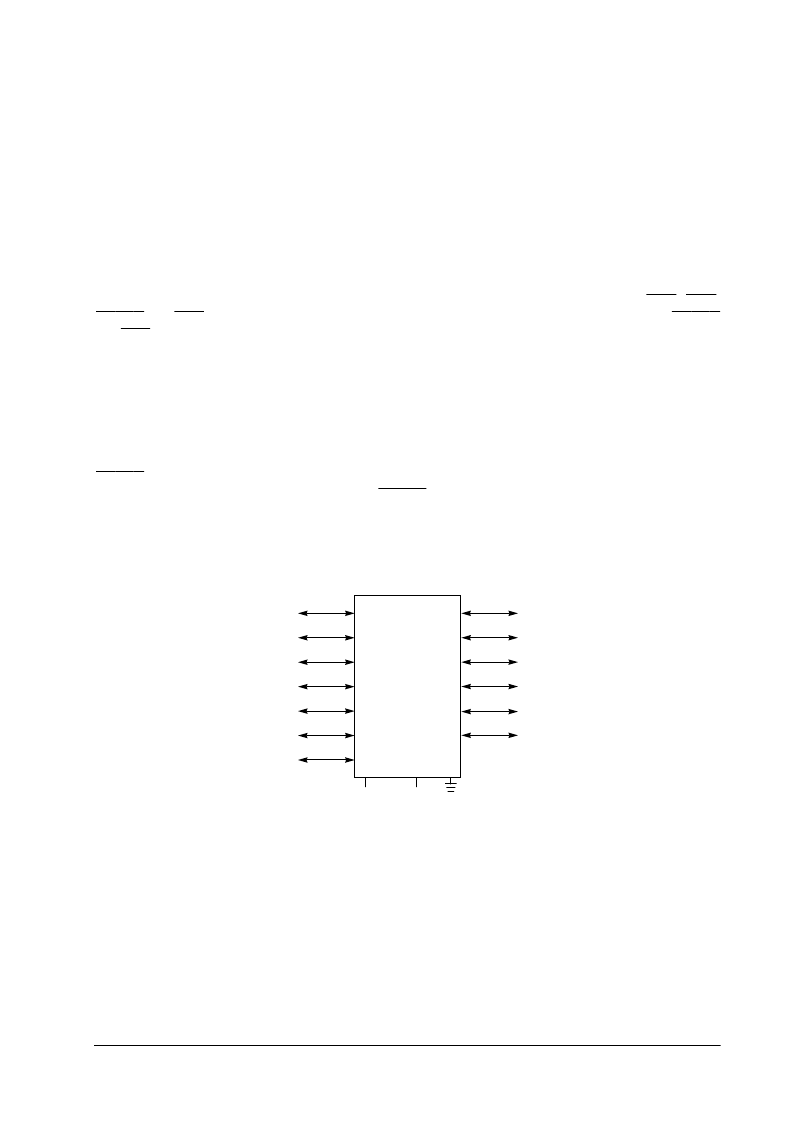

The system interface is specific for each PowerPC processor implementation. The 604e system interface is

shown in Figure 4.

Figure 4. System Interface

Four-beat burst-read memory operations that load an eight-word cache block into one of the on-chip caches

are the most common bus transactions in typical systems, followed by burst-write memory operations,

direct-store operations, and single-beat (noncacheable or write-through) memory read and write operations.

Additionally, there can be address-only operations, variants of the burst and single-beat operations (global

memory operations that are snooped and atomic memory operations, for example), and address retry

activity (for example, when a snooped read access hits a modified line in the data cache).

Memory accesses can occur in single-beat or four-beat burst data transfers. The address and data buses are

independent for memory accesses to support pipelining and split transactions. The 604e supports bus

pipelining and out-of-order split-bus transactions. In general, the bus-pipelining mechanism allows as many

+2.5 V

+3.3 V

PowerPC

604e

Processor

ADDRESS

ADDRESS ARBITRATION

ADDRESS START

ADDRESS TRANSFER

TRANSFER ATTRIBUTE

ADDRESS TERMINATION

CLOCKS

DATA

DATA ARBITRATION

DATA TRANSFER

DATA TERMINATION

PROCESSOR STATE

TEST AND CONTROL

相關PDF資料 |

PDF描述 |

|---|---|

| MPC755BPX350LE | RISC Microprocessor Hardware Specifications |

| MPC755BRX350LE | RISC Microprocessor Hardware Specifications |

| MPC755CPX400LE | RISC Microprocessor Hardware Specifications |

| MPC755CRX400LE | RISC Microprocessor Hardware Specifications |

| MPC755 | RISC Microprocessor Hardware Specifications |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MPC6071 | 制造商:International Rectifier 功能描述: |

| MPC616 | 制造商:Hammond Manufacturing 功能描述:6" X 16" MAGNET PANEL COVER |

| MPC-628-011B | 制造商:FCI 功能描述: |

| MPC628726C | 制造商:FCI 功能描述:- Bulk |

| MPC-6800 | 制造商:AAEON 制造商全稱:AAEON 功能描述:Intel Ultra Low Voltage Celeron Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復。