- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45215 > M68LC302CPU16VCT (FREESCALE SEMICONDUCTOR INC) 4 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | M68LC302CPU16VCT |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP100 |

| 封裝: | 14 X 14 MM, 1.40 MM HEIGHT, 0.50 MM PITCH, PLASITC, LQFP-100 |

| 文件頁數(shù): | 80/128頁 |

| 文件大?。?/td> | 641K |

| 代理商: | M68LC302CPU16VCT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁當前第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁

ETHERNET Controller

4-16

MC68EN302 REFERENCE MANUAL

MOTOROLA

4.2.2 ETHERNET TRANSMIT BUFFER DESCRIPTOR

Transmit data is presented to the Ethernet controller through buffers referenced by transmit

Buffer Descriptors. The Ethernet controller confirms transmission operation through the R

bit, and indicates error conditions through the other status bits in the most signficant word

of the BD. The host software must initialize the R, W, I, L, TC, and (optionally) TO bits in the

first word, the length in the second word, and the buffer pointer in the third and fourth words.

.

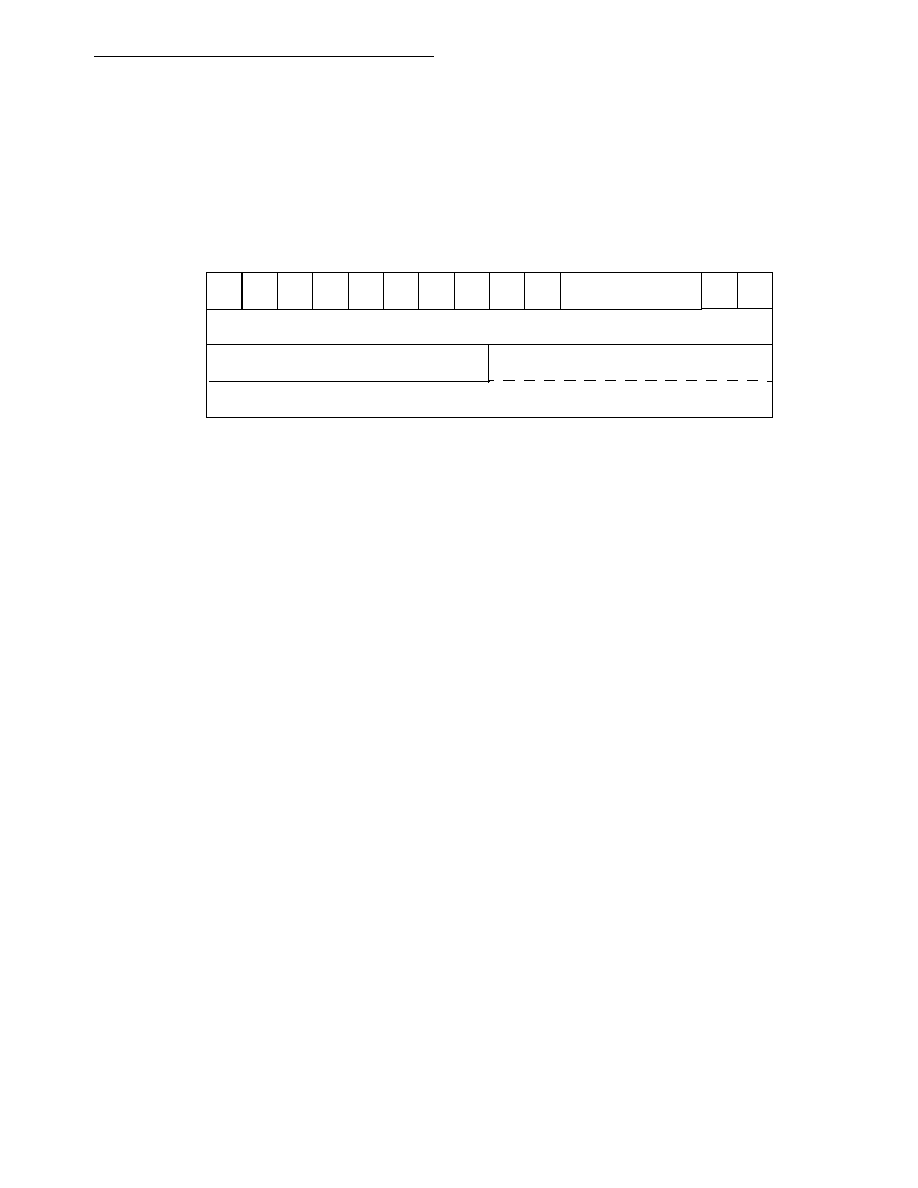

Figure 4-3. Ethernet Transmit Buffer Descriptor (Tx BD)

The Tx BD fields are detailed below. The unused bits (15-8) in Offset + 4 are not used by

the hardware. These unused bits are R/W by software and are ignored by hardware.

R—Ready, written by Ethernet controller and user.

0 = The data buffer associated with this BD is not ready for transmission, leaving the

software free to manipulate this BD or its associated data buffer. The Ethernet

controller clears this bit after the buffer has been transmitted or after an error

condition is encountered.

1 = The data buffer, which has been prepared for transmission by the user, has not

been transmitted or is currently being transmitted. No fields of this BD may be

written after this bit is set.

TO—Transmit Buffer Software Ownership, written by user.

This bit is provided as a software ownership bit, if needed. Hardware does not alter the value

of this bit.

L— Last (Last BD for this frame)

0 = This is not the last BD for this frame and the Ethernet controller sets R= 0 when the

buffer has been DMA’d into the MC68EN302. Status bits are not modified.

1 = The Ethernet controller sets R = 0 and modifies the DEF, HB, LC, RL, RC, UN and

CSL status bits once the buffer has been DMA’d into the MC68EN302 and frame

transmission has completed

Offset + 0

Offset + 2

Offset + 4

Offset + 6

Tx Data Buffer Pointer - A15–A0

Data Length

CSL

UN

RL

LC

TC

L

I

W

TO

R

HB

DEF

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

RC

A23–A16

Unused

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68LC302PU20VCT | 4 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP100 |

| MC68302CPV16VC | 4 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP144 |

| MC68LC302PU20VCT | 4 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP100 |

| MC68EN302CPV20BT | 4 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP144 |

| MC68302FC20CR2 | 4 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP132 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M68LC302CPU20VCT | 功能描述:IC MPU NETWORK 20MHZ 100-LQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:M683xx 標準包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| M68LGL061X | 制造商:Panasonic Industrial Company 功能描述:SUB ONLY CRT |

| M68LGL061XA | 制造商:Panasonic Industrial Company 功能描述:CRT OR M68LGL061X |

| M68LNK161X | 制造商:Panasonic Industrial Company 功能描述:CRT |

| M68LUQ085X | 制造商:Panasonic Industrial Company 功能描述:CRT |

發(fā)布緊急采購,3分鐘左右您將得到回復。