- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180051 > M-ORSO82G52BM680-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 1296 CLBS, 333000 GATES, PBGA680 PDF資料下載

參數(shù)資料

| 型號: | M-ORSO82G52BM680-DB |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| 封裝: | PLASTIC, FBGA-680 |

| 文件頁數(shù): | 98/123頁 |

| 文件大?。?/td> | 2207K |

| 代理商: | M-ORSO82G52BM680-DB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁當前第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁

Lattice Semiconductor

ORCA ORSO82G5 Data Sheet

76

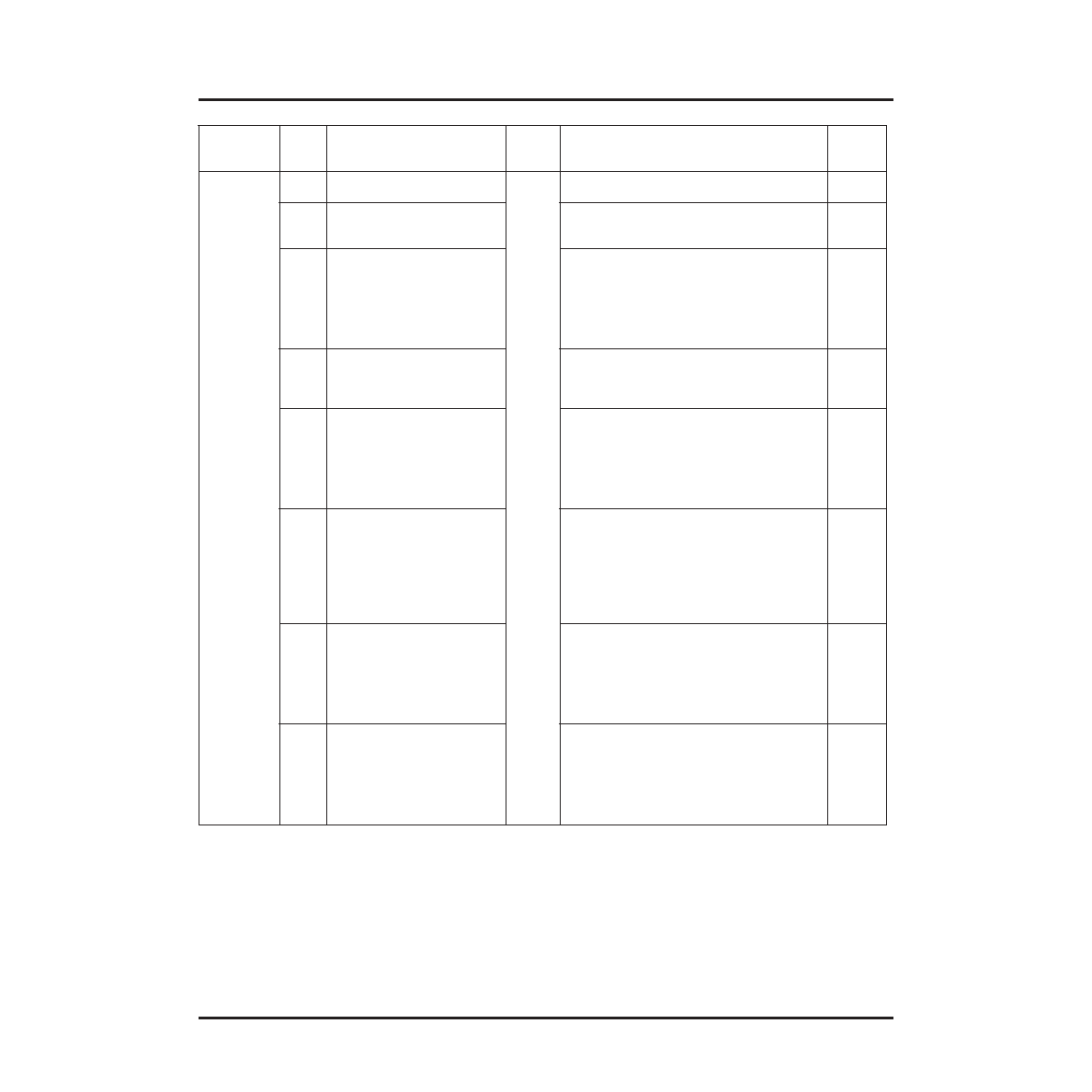

Table 19. Per-Channel Control Register Descriptions (continued)

(0x) Abso-

lute

Address

Bit

Name

Reset

Value

(0x)

Description

Mode

30804 - AA

30814 - AB

30824 - AC

30834 - AD

30904 - BA

30914 - BB

30924 - BC

30934 - BD

[0]

LCKREFN_xx

00

0 = Lock receiver to reference clock (REFCLK)

1 = Lock receiver to HDINxx data

Both

[1]

LOOPENB_xx

LOOPENB_xx =1 Enable high-speed internal

loopback from TX to RX. Disable the HDOUT

buffers.

Both

[2]

DISABLE_TX_xx

Disable Transmitter, For DISABLE_TX = 1 the

TX Link is disabled. The disabled link is ignored

by the Output Port Controller (OPC) and inter-

nally generated idle cells are transmitted on the

link.fIf the link is disabled during the transmis-

sion of a cell on the link, the entire cell is trans-

mitted before the link is declared invalid.

Cell

[3]

DISABLE_RX_xx

Disable Receiver, DISABLE_RX = 1 disables

the RX link for cell processing by the Input Port

Controller (IPC). The IPC will not read cells

from a link if this bit is set for that link

Cell

[4]

CELL_BIP_INH_xx

Cell BIP (Check) Inhibit, CELL_BIP_INH = 1

prevents cells from being dropped due to a Cell

BIP error, in the RX path. If this bit is not set,

then cells will be dropped automatically if a cell

bip error is detected by the core. The CELL-

DROP signal across the core-FPGA interface

will be active only if this bit is NOT set.

Cell

[5]

CELL_SEQ_INH_xx

Cell Sequence (Checking) Inhibit,

CELL_SEQ_INH = 1 prevents cells in the RX

path from being dropped due to a sequence

error. If this bit is not set, then cells will be

dropped automatically if a sequence error is

detected internally. The CELLDROP signal

across the core-FPGA interface will be active

only if this bit is NOT set.

Cell

[6]

AUTO_TOH_xx

Automatic TOH Generation, AUTO_TOH_xx =1

enables the TX core to automatically generate

TOH bytes. All the FORCE_* register bits are

valid only if this bit is set. This bit should be set

to 1 in Cell Mode. It can be set to 1or 0 in

SONET Mode. If this bit is not set, then user

has to provide all the TOH bytes.

SONET

[7]

FMPU_RESYNC1_xx

Single channel alignment FIFO reset. Rising

edge sensitive. Write a 0 and then a 1 to enable

this bit. When enabled, the read pointer in the

alignment FIFO is reset to the middle of the

FIFO. This bit is valid only when

FMPU_SYNMODE_xx = 00 (no multi channel

alignment)

SONET

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M-ORT82G51BM680-DB | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| M-ORT82G52BM680-DB | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| M.PI-1R1D12 | 1 ELEMENT, 1.1 uH, GENERAL PURPOSE INDUCTOR, SMD |

| M01-014-1452PA | 14 CONTACT(S), MALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SOLDER |

| M01-016-1443PA | 16 CONTACT(S), MALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SOLDER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MORTAR-44LB | 制造商:3M Electronic Products Division 功能描述:3M(TM) FIRE BARRIER MORTAR, 44 98040056073 制造商:3M Electronic Products Division 功能描述:Fire Barrier 44 lb Bag |

| MO-RX3930 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS315M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS434M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FSK RECEIVER MODULE |

發(fā)布緊急采購,3分鐘左右您將得到回復。