- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373155 > KM416S1020C (SAMSUNG SEMICONDUCTOR CO. LTD.) 512K x 16Bit x 2 Banks Synchronous DRAM(512K x 16位 x 2組同步動(dòng)態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號(hào): | KM416S1020C |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 512K x 16Bit x 2 Banks Synchronous DRAM(512K x 16位 x 2組同步動(dòng)態(tài)RAM) |

| 中文描述: | 為512k × 16 × 2銀行同步DRAM(為512k × 16位× 2組同步動(dòng)態(tài)RAM)的 |

| 文件頁(yè)數(shù): | 19/42頁(yè) |

| 文件大?。?/td> | 582K |

| 代理商: | KM416S1020C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)

CMOS SDRAM

DEVICE OPERATIONS - I

ELECTRONICS

REV. 4 Feb. '98

*Note :

1. t

RDL

: Last data in to row precharge delay

2. Number of valid output data after row precharge : 0, 1, 2 for CAS Latency =1, 2, 3 respectively.

3. The row active command of the precharge bank can be issued after t

The new read/write command of the other activated bank can be issued from this point.

At burst read/write with auto precharge, CAS interrupt of the same/other bank is illegal.

RP

from this point.

6. Precharge

D

0

D

1

D

2

CLK

CMD

DQ

WR

PRE

D

3

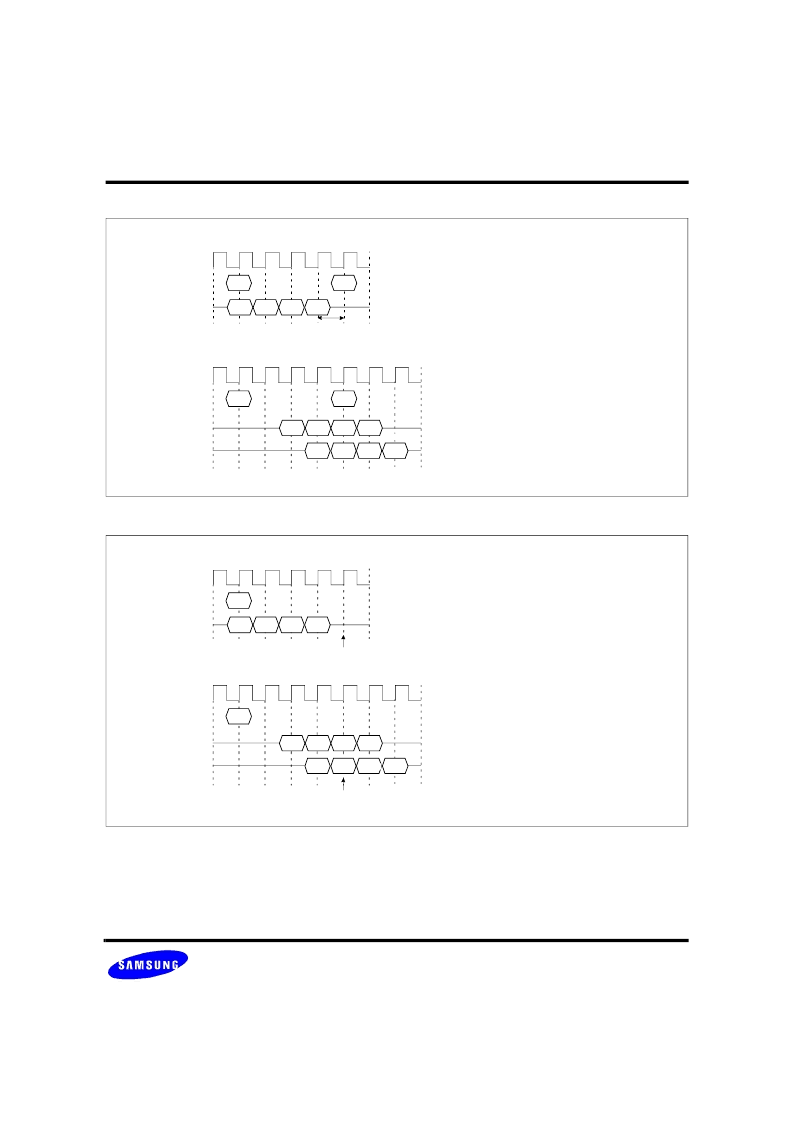

1) Normal Write (BL=4)

tRDL

Note 2

2) Normal Read (BL=4)

CLK

CMD

DQ(CL2)

DQ(CL3)

RD

PRE

Q

0

Q

1

Q

2

Q

3

Q

0

Q

1

Q

2

Q

3

1

2

Note 2

7. Auto Precharge

D

0

D

1

D

2

CLK

CMD

DQ

WR

D

3

1) Normal Write (BL=4)

Note 3

Auto Precharge Starts

2) Normal Read (BL=4)

CLK

CMD

DQ(CL2)

DQ(CL3)

RD

Q

0

Q

1

Q

2

Q

3

Q

0

Q

1

Q

2

Q

3

Note 3

Auto Precharge Starts

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KM416S1021C | 512K x 16Bit x 2 Banks Synchronous DRAM with SSTL interfacer(512K x 16位 x 2組同步動(dòng)態(tài)RAM(帶SSTL接口)) |

| KM416S4020B | 2M x 16Bit x 2 Banks Synchronous DRAM(2M x 16位 x2組同步動(dòng)態(tài)RAM) |

| KM416S4021B | 2M x 16Bit x 2 Banks Synchronous DRAM(2M x 16位 x2組同步動(dòng)態(tài)RAM) |

| KM416S4030B | 1M x 16Bitx 4 Banks Synchronous DRAM(1M x 16位 x4組同步動(dòng)態(tài)RAM) |

| KM416S4031B | 1M x 16Bit x 4 Banks Synchronous DRAM with SSTL interface(1M x 16位 x4組同步動(dòng)態(tài)RAM(帶SSTL接口)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KM416S1020CTG10 | 制造商:n/a 功能描述:KM416S1020CT-G10 制造商:Samsung Semiconductor 功能描述: |

| KM416S1020CT-G10 | 制造商:n/a 功能描述:KM416S1020CT-G10 制造商:Samsung Semiconductor 功能描述: |

| KM416S1020CT-G10M | 制造商:MAJOR 功能描述: |

| KM416S1021C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512K x 16Bit x 2 Banks Synchronous DRAM with SSTL interface |

| KM416S1021CT-G7 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512K x 16Bit x 2 Banks Synchronous DRAM with SSTL interface |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。