- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370782 > HYB18T512160AF-3 (INFINEON TECHNOLOGIES AG) 512-Mbit DDR2 SDRAM PDF資料下載

參數(shù)資料

| 型號(hào): | HYB18T512160AF-3 |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 512-Mbit DDR2 SDRAM |

| 中文描述: | 512兆位DDR2 SDRAM的 |

| 文件頁數(shù): | 65/117頁 |

| 文件大?。?/td> | 2102K |

| 代理商: | HYB18T512160AF-3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁當(dāng)前第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁

Data Sheet

65

Rev. 1.3, 2005-01

09112003-SDM9-IQ3P

HYB18T512[40/80/16]0AF–[3/3S/3.7/5]

512-Mbit DDR2 SDRAM

Functional Description

3.23.2

Write with Auto-Precharge

If A10 is HIGH when a Write Command is issued, the

Write with Auto-Precharge function is engaged. The

DDR2 SDRAM automatically begins precharge

operation after the completion of the write burst plus the

write recovery time delay (WR), programmed in the

MRS register, as long as

t

RAS

is satisfied. The bank

undergoing Auto-Precharge from the completion of the

write burst may be reactivated if the following two

conditions are satisfied.

1. The last data-in to bank activate delay time (

t

DAL

=

WR +

t

RP

) has been satisfied.

2. The RAS cycle time (

t

RC

) from the previous bank

activation has been satisfied.

In DDR2 SDRAM’s the write recovery time delay (WR)

has to be programmed into the MRS mode register. As

long as the analog

t

WR

timing parameter is not violated,

WR can be programmed between 2 and 6 clock cycles.

Minimum Write to Activate command spacing to the

same bank = WL + BL/2 +

t

DAL

.

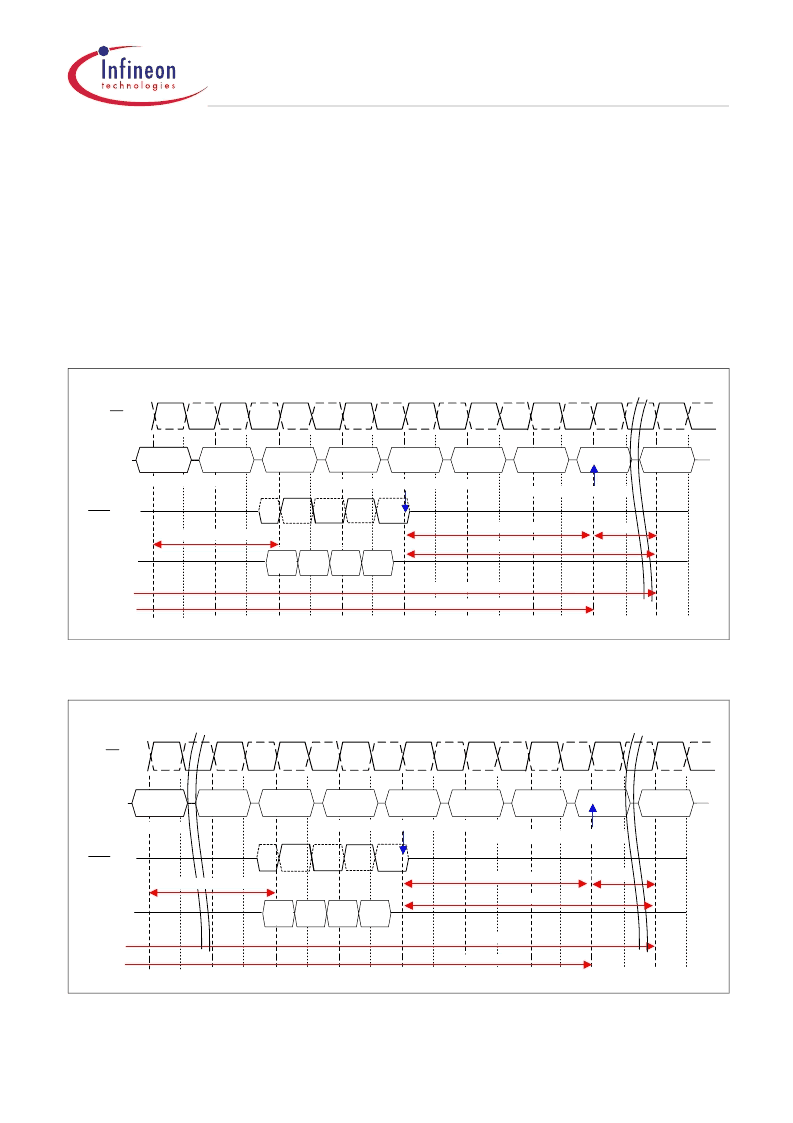

Figure 51

Write with Auto-Precharge Example 1 (

t

RC

Limit)

WL = 2,

t

DAL

= 6 (WR = 3,

t

RP

= 3), BL = 4

Figure 52

Write with Auto-Precharge Example 2 (WR +

t

RP

Limit)

WL = 4,

t

DAL

= 6 (WR = 3,

t

RP

= 3), BL = 4

NOP

NOP

NOP

NOP

NOP

Bank A

Activate

NOP

W RITE

w/AP

T0

T2

T1

T3

T4

T5

T6

T7

NOP

CMD

DQ

BW-AP223

A10 ="high"

tRP

Auto-Precharge Begins

DIN A0 DIN A1 DIN A2 DIN A3

WL = RL-1 = 2

WR

tRCmin.

>=tRASmin.

DQS,

DQS

Completion of the Burst Write

tDAL

CK, CK

NOP

NOP

NOP

NOP

NOP

Bank A

Activate

NOP

W RITE w/AP

Posted CAS

T0

T3

T4

T5

T6

T7

T12

NOP

CMD

DQ

BW-AP423

A10 ="high"

tRP

Auto-Precharge Begins

DIN A0 DIN A1 DIN A2 DIN A3

WL = RL-1 = 4

WR

>=tRC

T9

T8

Completion of the Burst Write

DQS,

DQS

tDAL

>=tRAS

CK, CK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB18T512160AF-3.7 | 512-Mbit DDR2 SDRAM |

| HYB18T512160AF-3S | 512-Mbit DDR2 SDRAM |

| HYB18T512400AF-3 | 512-Mbit DDR2 SDRAM |

| HYB18T512400AF-3S | 512-Mbit DDR2 SDRAM |

| HYB18T512800AF-3 | 512-Mbit DDR2 SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB18T512161BF-25 | 制造商:Qimonda 功能描述:SDRAM, DDR, 32M x 16, 84 Pin, Plastic, BGA |

| HYB18T512400AF-5 | 制造商:Intersil Corporation 功能描述:SDRAM, DDR, 128M x 4, 60 Pin, Plastic, BGA |

| HYB18T512400BF-3S | 制造商:Qimonda 功能描述: |

| HYB18T512800AF-3S | 制造商:Qimonda 功能描述: 制造商:Infineon Technologies AG 功能描述:32M X 16 DDR DRAM, 0.45 ns, PBGA84 |

| HYB18T512800BF-2.5 | 功能描述:IC DDR2 SDRAM 512MBIT 60TFBGA RoHS:是 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:60 系列:- 格式 - 存儲(chǔ)器:EEPROMs - 串行 存儲(chǔ)器類型:EEPROM 存儲(chǔ)容量:16K (2K x 8) 速度:2MHz 接口:SPI 3 線串行 電源電壓:2.5 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 封裝/外殼:8-DIP(0.300",7.62mm) 供應(yīng)商設(shè)備封裝:8-PDIP 包裝:管件 產(chǎn)品目錄頁面:1449 (CN2011-ZH PDF) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。