- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370499 > HDMP-1014 Bipolar Transistor; Collector Emitter Voltage, Vceo:400V; Transistor Polarity:N Channel; Power Dissipation:250W; C-E Breakdown Voltage:400V; DC Current Gain Min (hfe):10; Collector Current:50A; Package/Case:TO-3 PDF資料下載

參數(shù)資料

| 型號: | HDMP-1014 |

| 英文描述: | Bipolar Transistor; Collector Emitter Voltage, Vceo:400V; Transistor Polarity:N Channel; Power Dissipation:250W; C-E Breakdown Voltage:400V; DC Current Gain Min (hfe):10; Collector Current:50A; Package/Case:TO-3 |

| 中文描述: | 4Low成本千兆速率發(fā)送/接收芯片組 |

| 文件頁數(shù): | 28/42頁 |

| 文件大小: | 321K |

| 代理商: | HDMP-1014 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

600

performed if the frame is a fill

frame.

The Output Select block allows

the user to select between two

sets of differential high speed

serial outputs. This feature is

useful for loop back testing. If

LOOPEN is high, LOUT is enabled

and DOUT is disabled. If LOOPEN

is low, DOUT is enabled and

LOUT is disabled.

The active-low RST* input resets

the internal registers to a

balanced state. This pin should be

held low for at least five frame

rate clock cycles to ensure a

complete reset.

The Data Field and Control Field

are encoded depending on ED,

FF, DAV*, CAV*, FLAG,

FLAGSEL, M20SEL as well as two

internally generated signals, O/E

and ACCMSB.

When FLAGSEL is high, O/E is

equivalent to FLAG. This is

equivalent to adding an additional

bit to the data field. When

FLAGSEL is low, O/E alternates

between high and low for data

frames. This allows the link to

perform more extensive error

detection when the extra bit is

unused.

ACCMSB is the sign of the

previously transmitted data. This

is used to determine which type of

FF1 should be sent. When

ACCMSB is low, FF1a is sent and

when ACCMSB is high, FF1b is

sent. This effectively drives the

accumulated offset of transmitted

bits back toward the balanced

state.

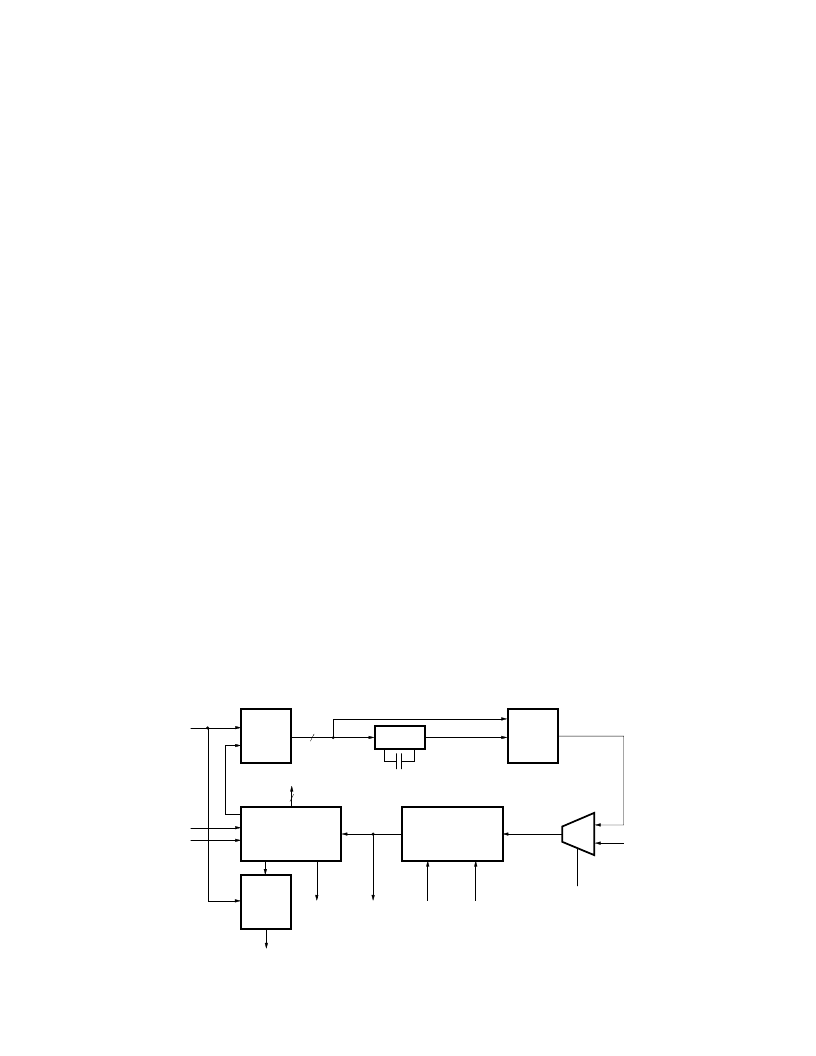

Tx Phase-Locked Loop

The block diagram of the

transmitter phase-locked loop is

shown in Figure 12. It consists of

a sequential frequency detector,

loop filter, VCO, clock generation

circuitry, and a lock indicator.

The outputs of the frequency

detector pass through a charge

pump filter that controls the

center frequency of the VCO.

These outputs also go to the VCO

directly to effectively add a zero

in the loop response. An external

high-speed clock can be used

instead of the VCO clock. This is

accomplished by applying a high

signal to EHCLKSEL and a

differential clock to STRBIN.

One of four frequency bands may

be selected by applying

appropriate inputs to DIV0 and

DIV1. The VCO or STRBIN

frequency is divided by N, where

N is 1, 2, 4, or 8 corresponding to

the binary number represented by

DIV1, DIV0. This divided version

of the VCO clock or STRBIN is

used as the serial rate clock and is

available as a differential signal at

the HCLK output.

A clock generator block creates

all the clock signals required for

the chip. Depending on M20SEL,

STRBOUT is either HCLK/20 or

HCLK/24. If MDFSEL is low, then

STRBOUT is a phase-locked

version of STRBIN. If MDFSEL is

high, STRBOUT is twice the

frequency of STRBIN.

Figure 12. HDMP-1012 (Tx) Phase-Locked Loop.

FREQ

DETECT

STRBIN

GCLOCK

LOCK

DIV N

FILTER

VCO

EHCLKSEL

STRBIN

1

0

DIV0

DIV1

LOCKED

STRBOUT

INTERNAL CLOCKS

M20SEL

MDFSEL

HCLK

相關PDF資料 |

PDF描述 |

|---|---|

| HDMP-1022 | Audio Power Amplifier; Speaker Channels:Mono; Headphone Channels:Mono; Output Power, Po:2W; Load Impedance Min:8ohm; Supply Voltage Max:24V; Supply Voltage Min:6V |

| HDMP-1024 | Low Cost Gigabit Rate Receive Chip Set with TTL I/Os(帶TTL輸入/輸出的低價格千兆位速率接收芯片) |

| HDMP-1032 | 1.4 GBd Transmitter Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 傳送器) |

| HDMP-1034 | 1.4 GBd Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 接收器) |

| HDMP-1512 | Fibre Channel Transmitter Chipset(光纖通道傳送芯片) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1022 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1024 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1032 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1032A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:1.4 GBd Transmitter Chip with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

發(fā)布緊急采購,3分鐘左右您將得到回復。