- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370499 > HDMP-1014 Bipolar Transistor; Collector Emitter Voltage, Vceo:400V; Transistor Polarity:N Channel; Power Dissipation:250W; C-E Breakdown Voltage:400V; DC Current Gain Min (hfe):10; Collector Current:50A; Package/Case:TO-3 PDF資料下載

參數(shù)資料

| 型號: | HDMP-1014 |

| 英文描述: | Bipolar Transistor; Collector Emitter Voltage, Vceo:400V; Transistor Polarity:N Channel; Power Dissipation:250W; C-E Breakdown Voltage:400V; DC Current Gain Min (hfe):10; Collector Current:50A; Package/Case:TO-3 |

| 中文描述: | 4Low成本千兆速率發(fā)送/接收芯片組 |

| 文件頁數(shù): | 20/42頁 |

| 文件大小: | 321K |

| 代理商: | HDMP-1014 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

592

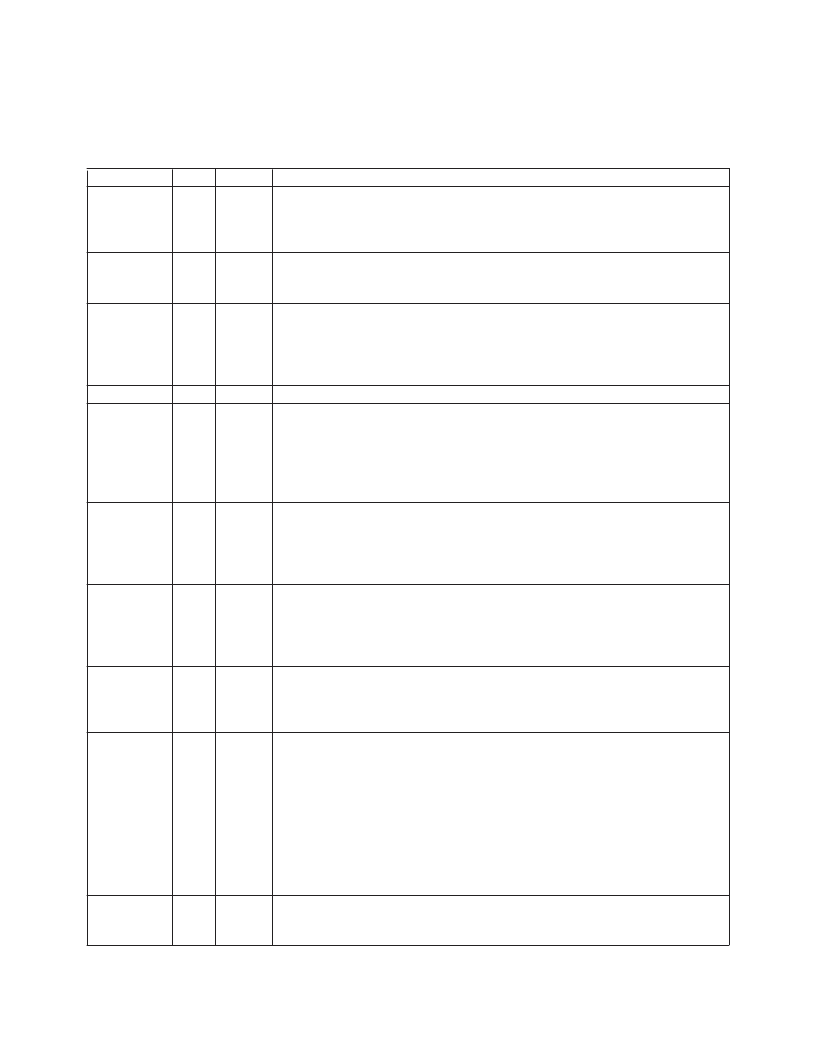

Rx I/O Definition (cont’d.)

Name

ECLGND

Pin

32

52

53

72

19

Type

S

Signal

ECL Ground:

Normally 0 volts. This ground is used for the ECL pad

drivers. For best performance it is suggested that coupling of the noisy

ECLGND to the clean GND and HGND grounds be minimized.

EQEN

I-ECL

Enable Input for Cable Equalization:

When asserted, this signal

activates the cable equalization amplifier on the DIN, DIN* serial

data inputs.

Received Data Error:

Asserted when a frame is received that does

not correspond to either a

valid

Data, Control, or Fill frame encoding.

When FLAGSEL is not active, the Rx chip also tests for strict

alternation of flag bits during data frames. A flag bit alternation

error will also cause an ERROR indication.

Frame Clock Monitor:

Leave unterminated in normal use.

Frequency Detector Disable Input:

When active, this input

disables the Rx PLL Frequency detector and enables a phase detector.

The Frequency detector is used during the start-up sequence to

acquire wide-band lock on Fill Frames, but must be disabled prior to

sending data patterns. This input is normally controlled by the Rx

state machine.

Fill Frame Status:

During a given STRBOUT clock cycle, if neither

DAV, CAV, or ERROR are active, then the currently received frame

is a Fill frame. The type of fill frame received is indicated by the FF

pin. If FF is low, then FF0 has been received. If FF is high, then

either FF1a or FF1b has been received.

Flag Bit:

If both Tx and Rx have FLAGSEL asserted, this output

indicates the value of the transmitted flag bit, then this received bit

can be treated just like an extra data bit. If both Tx and Rx have

FLAGSEL set to low, FLAG is used to differentiate the even frame

from the odd frame in the line code.

Flag Bit Mode Select:

When this input is high, the extra FLAG bit

output is effectively an extra transparent data bit. Otherwise, the

FLAG bit is checked for alternation during data frames. Any break in

strict alternation results in an ERROR indication to the user.

Ground:

Normally 0 volts. This ground is used for all the core logic

other than the output drivers.

ERROR

40

O-ECL

FCLK

FDIS

75

20

O-ECL

I-ECL

FF

39

O-ECL

FLAG

45

O-ECL

FLAGSEL

34

I-ECL

GND

5

23

24

33

43

44

63

64

73

78

13

S

HGND

S

High Speed Ground:

Normally 0 volts. This ground is used to

provide clean references for the high speed DIN, DIN*, LIN, LIN*,

TCLK, TCLK* inputs.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1022 | Audio Power Amplifier; Speaker Channels:Mono; Headphone Channels:Mono; Output Power, Po:2W; Load Impedance Min:8ohm; Supply Voltage Max:24V; Supply Voltage Min:6V |

| HDMP-1024 | Low Cost Gigabit Rate Receive Chip Set with TTL I/Os(帶TTL輸入/輸出的低價格千兆位速率接收芯片) |

| HDMP-1032 | 1.4 GBd Transmitter Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 傳送器) |

| HDMP-1034 | 1.4 GBd Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 接收器) |

| HDMP-1512 | Fibre Channel Transmitter Chipset(光纖通道傳送芯片) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1022 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1024 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1032 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1032A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:1.4 GBd Transmitter Chip with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。