- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370499 > HDMP-1014 Bipolar Transistor; Collector Emitter Voltage, Vceo:400V; Transistor Polarity:N Channel; Power Dissipation:250W; C-E Breakdown Voltage:400V; DC Current Gain Min (hfe):10; Collector Current:50A; Package/Case:TO-3 PDF資料下載

參數(shù)資料

| 型號: | HDMP-1014 |

| 英文描述: | Bipolar Transistor; Collector Emitter Voltage, Vceo:400V; Transistor Polarity:N Channel; Power Dissipation:250W; C-E Breakdown Voltage:400V; DC Current Gain Min (hfe):10; Collector Current:50A; Package/Case:TO-3 |

| 中文描述: | 4Low成本千兆速率發(fā)送/接收芯片組 |

| 文件頁數(shù): | 24/42頁 |

| 文件大?。?/td> | 321K |

| 代理商: | HDMP-1014 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

596

Appendix I: Additional

Internal Architecture

Information

Line Code Description

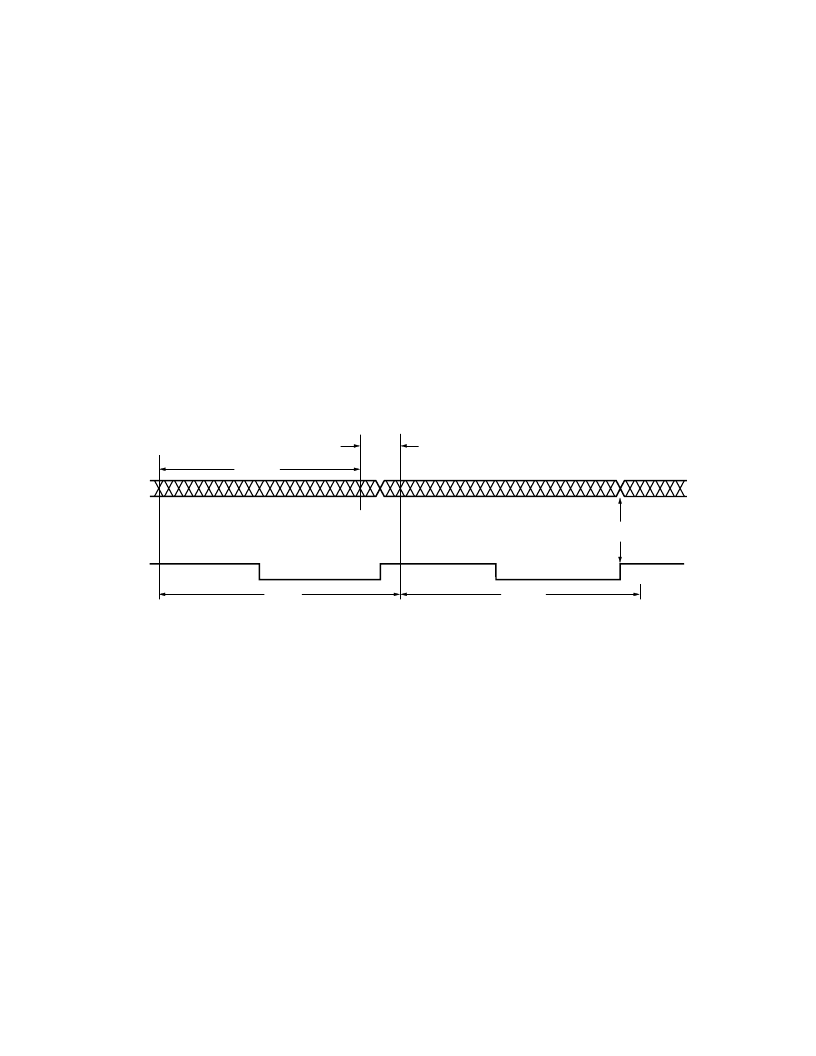

The HDMP-1012/1014 line code

is Conditional Invert Master

Transition (CIMT), illustrated in

Figure 11. The CIMT line uses

three types of frames: data

frames, control frames, and fill

frames. Fill frames are internally

generated by the Tx chip for use

during link start up and when

there is no input from the user.

Each frame consists of a Data

Field (D-Field) followed by a

Coding Field (C-Field). The D-

Field can be either 16-bits or 20-

bits wide, depending on link

configuration. The C-Field has a

master transition which serves as

a fixed timing reference for the

receivers clock recovery circuit.

Users can send arbitrary data

carried by Data or Control

Frames. The dc balance of the

line code is automatically

enforced by the Tx. Fill frames

have a single rising edge at the

master transition which is used

for clock recovery and frame

synchronization at the receiver.

Detailed coding schemes are

described in the following

subsections. All the tables given

in this section show data bits in

the same configuration as a scope

display. In other words, the

leftmost bit in each table is the

first bit to be transmitted in time,

while the rightmost bit is the last

bit to be transmitted.

Data Frame Codes

When not in FLAGSEL mode, the

FLAG bit is not user controllable

and is alternately sent as 0 and 1

by the Tx chip during data frames

to provide enhanced error

detection. Control and Fill frames

do not cause toggling between

even and odd frames to occur

(The FLAG bit is not available

during control frames). The

receiver performs a differential

detection to make sure that every

data frame received is the

opposite pattern from the

previous frame. If a break in the

strict alternation is observed, a

frame error is flagged by

asserting the Rx ERROR output.

This pattern detection makes it

impossible for a static input data

pattern to generate an

undetectable false lock point in

the transmitted data stream. The

detection also reduces the

probability that the loop could

lock onto random data at a point

away from the true master

transition for any significant time

before it would be detected as a

false lock. This mode can detect

all single-bit errors in the C-field

(non-data bit fields) of the frame.

When the chip is in FLAGSEL

mode, the extra FLAG bit is freely

user definable as an extra data

bit. This provides a 17th bit in 16

bit mode, and a 21st bit in 20 bit

mode. The probability of

undetected false lock is higher,

but the users (e.g., SCI-FI) that

need the extra bit can detect false

lock at a higher level of the

network protocol with clock

recovery circuits, etc. If the

higher level protocols consistently

receive wrong data, they can

initiate a link restart by resetting

the Rx state machine.

Figure 11. HDMP-1012/1014 (Tx/Rx Pair) Line Code.

DATA FIELD

16/20 BITS

CODING FIELD

4 BITS

FILL

FRAME

SERIAL

DATA

FRAME K

FRAME K+1

MASTER

TRANSITION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1022 | Audio Power Amplifier; Speaker Channels:Mono; Headphone Channels:Mono; Output Power, Po:2W; Load Impedance Min:8ohm; Supply Voltage Max:24V; Supply Voltage Min:6V |

| HDMP-1024 | Low Cost Gigabit Rate Receive Chip Set with TTL I/Os(帶TTL輸入/輸出的低價格千兆位速率接收芯片) |

| HDMP-1032 | 1.4 GBd Transmitter Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 傳送器) |

| HDMP-1034 | 1.4 GBd Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 接收器) |

| HDMP-1512 | Fibre Channel Transmitter Chipset(光纖通道傳送芯片) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1022 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1024 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1032 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1032A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:1.4 GBd Transmitter Chip with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。