- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379645 > ADM7008 (Electronic Theatre Controls, Inc.) Octal Ethernet 10/100M PHY PDF資料下載

參數(shù)資料

| 型號: | ADM7008 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Octal Ethernet 10/100M PHY |

| 中文描述: | 八路個10/100M以太網(wǎng)物理層 |

| 文件頁數(shù): | 26/92頁 |

| 文件大?。?/td> | 981K |

| 代理商: | ADM7008 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

ADM7008

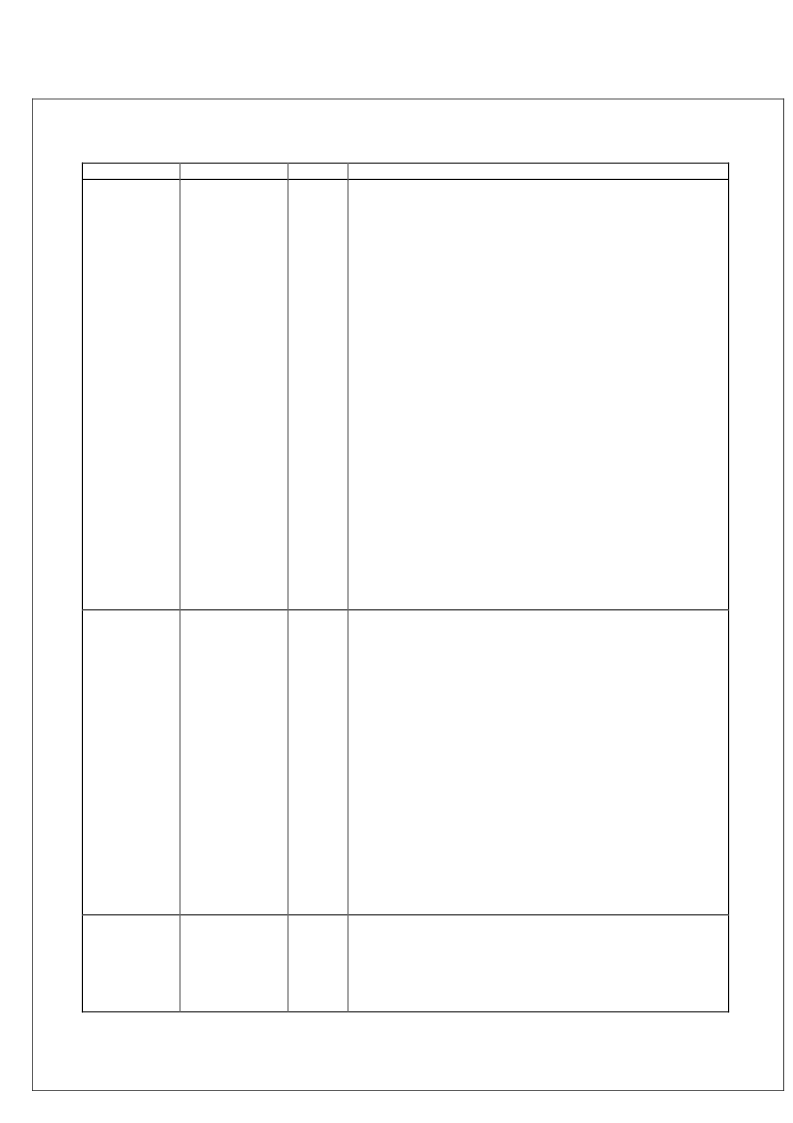

Interface Description

Pin #

Pin Name

Setting

SELFX1

RMII Mode

CRSDV_P1

SMII/SS_SMII

Mode

N/A

RMII Mode

TXD[1:0]_P1

SMII Mode

LNKACT_P1,

SMII_TXD_P1

SS_SMII Mode

LNKACT_P1,

SSSMII_TXD_P1

Type

8mA

PD

Pin Description

latched by ADM7008 during power on reset as fiber/twisted pair

interface configuration bit 1. Combined with SELFX0 (Power

On setting value on RXD0_P0) to program ADM7008 into 4

different modes.

00: all ports are twisted ports

01: only port 7 is fiber port, and all the other ports are twisted

ports.

10: only port 7 and port 6 are fiber ports, and all the other port

are twisted

port

11: all ports are fiber ports.

Port 1 Carrier Sense/Receive Data Valid. CRSDV_P1 asserts

when the receive medium is non-idle. The assertion of

CRSDV_P1 is asynchronous to REFCLK. At the de-assertion

of carrier, CRSDV_P1 de-asserts synchronously to REFCLK

only on the first di-bit of RXD. If there is still data in the FIFO

not yet presented onto RXD, then on the second di-bit of RXD,

CRSDV_P1 is asserted synchronously to REFCLK. The

toggling of CRSDV_P1 on the first and second di-bit continues

until all the data in the FIFO is presented onto RXD.

CRSDV_P1 is asserted for the duration of carrier activity for a

false carrier event.

Not Used.

Not used in SMII and SS_SMII Mode

ADMtek Inc.

2-14

98, 99

I,

TTL,

PD

Port 1 RMII Transmit Data. Transmit data for port 1 inputs the

di-bits that re transmitted and are driven synchronously to

REFCLK. Note that in 100Mb/s mode, TXD can change once

per REFCLK cycle, whereas in 10Mb/s mode, TXD must be

held steady for 10 consecutive REFCLK cycles.

Link and Activity LED/Port 1 SMII Transmit Data. TXD0 for port

1 inputs the data that is transmitted and is driven synchronously

to SMII_REFCLK (pin 70). In 100Mb/s mode, TXD0 inputs a

new 10-bit segment starting with SYNC. In 10Mb/s mode,

TXD0 must repeat each 10-bit segment 10 times.

TXD1_P1 acts as Port 1 Link/Activity LED in both SMII and

SS_SMII Mode. See LED Description for more detail.

Link and Activity LED/Port 1 SS_SMII Transmit Data. TXD0 for

port 1 inputs the data that is transmitted and is driven

synchronously to TXCLK (pin 70). In 100Mb/s mode, TXD0

inputs a new 10-bit segment starting with SYNC. In 10Mb/s

mode, TXD0 must repeat each 10-bit segment 10 times.

Port 1 Transmit Enable. Transmit Enable for port 1 indicates

that the di-bit on TXD is valid and it is driven synchronously to

REFCLK.

Not Used. Tied to LOW for normal operation in SMII/SS_SMII

mode.

100

RMII Mode

TXEN_P1

SMII/SS_SMII

LOW

I,

TTL

相關PDF資料 |

PDF描述 |

|---|---|

| ADM9511 | LAN/Modem Controller with Embedded Fast Ethernet PHY |

| ADS-238Q | 12-Bit, 20MHz, Low Power Sampling A/D Converters |

| ADS-917GC | 14-Bit, 1MHz, Low-Power Sampling A/D Converters |

| ADS-927GC | 14-Bit, 1MHz, Low-Power Sampling A/D Converters |

| ADS-927GM | 14-Bit, 1MHz, Low-Power Sampling A/D Converters |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ADM7008A3T1 | 功能描述:IC SWITCH CTRLR 10/100 128PQFP RoHS:否 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標準包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應商設備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| ADM7008A3T1NP | 制造商:Infineon Technologies AG 功能描述:SWITCH / PHY |

| ADM7008XA3T1 | 功能描述:IC SWITCH CTRLR 10/100 128PQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標準包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應商設備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| adm7008x-a3-t-1 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Infineon Technologies AG 功能描述: |

| ADM7008XA3T1XP | 制造商:Infineon Technologies AG 功能描述:GREEN, SWITCH / PHY |

發(fā)布緊急采購,3分鐘左右您將得到回復。