- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25056 > 0W888-002-XTP (ON SEMICONDUCTOR) BelaSigna 250 - 16 bit Audio Processor, Full Stereo 2-in, 2-out; Package: LFBGA 64, 7x7; No of Pins: 64; Container: Tape and Reel; Qty per Container: 1500 PDF資料下載

參數(shù)資料

| 型號: | 0W888-002-XTP |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | BelaSigna 250 - 16 bit Audio Processor, Full Stereo 2-in, 2-out; Package: LFBGA 64, 7x7; No of Pins: 64; Container: Tape and Reel; Qty per Container: 1500 |

| 中文描述: | 0-BIT, 50 MHz, MIXED DSP, PBGA64 |

| 封裝: | 7 X 7 MM, GREEN, LFBGA-64 |

| 文件頁數(shù): | 13/34頁 |

| 文件大小: | 935K |

| 代理商: | 0W888-002-XTP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

Rev. 7 | Page 20 of 34 | www.onsemi.com

BelaSigna 250

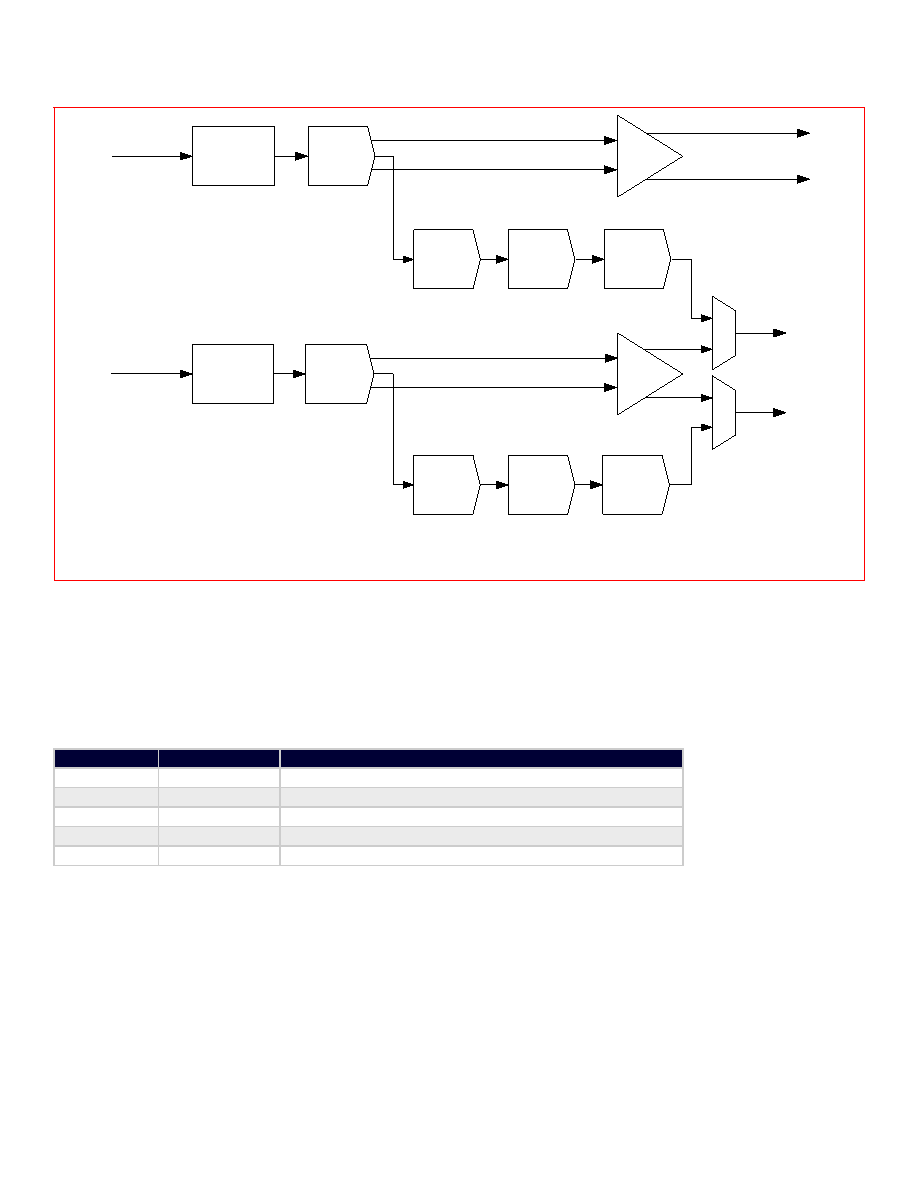

Output

Modulator

Interpolation

Filter

CH0 from

RCore/WOLA

RCVR0+

RCVR0-

D/A

Converter

LP

Filter

Output

Modulator

Interpolation

Filter

CH1 from

RCore/WOLA

AO0/RCVR1+

D/A

Converter

LP

Filter

AO1/RCVR1-

A

M

U

X

A

M

U

X

Direct

Drive

Direct

Drive

Attenuator

Figure 11: Output Stage

3.5.3. Clock-Generation Circuitry

The chip operates with five clock domains to provide flexibility in the control of peripherals, the selection of sampling frequencies and

the configuration of interface communication speeds. The five clock domains are as follows in Table 9. The base clock for all operations

on the BelaSigna 250 chip is the system clock (SYS_CLK). This clock may be acquired from one of three sources: the main on-chip

oscillator, the system standby clock or an external clock signal.

Table 9: Clock Domains

Clock Name

Description

Used For

SYS_CLK

System clock

All on-chip processors such as RCore, WOLA, IOP

MCLK

Main clock

All A/D and D/A converters

PCLK

Peripheral clock

Debug port, remote control, watchdog timer

WOLACLK

WOLA clock

WOLA module computations

UCLK

User clock

Can be programmed to provide a dedicated clock for an external device

The internal RC oscillator is characterized to operate up to a frequency of 5.12MHz. To operate properly using this internal clock,

BelaSigna 250 has to be calibrated, and the calibration values are to be stored within a non-volatile memory (usually an SPI EEPROM).

When calibration isn’t possible, BelaSigna 250 can operate with an externally supplied SYS_CLK, in this case, it is qualified for

operation up to 50MHz.

The sampling frequency for all A/D and D/A converters depends on MCLK. When MCLK is 1.28MHz, sampling frequencies up to

20kHz can be selected. When MCLK is 1.92MHz sampling frequencies up to 30kHz can be selected. For MCLK equal to 2.56MHz

sampling frequencies up to 40kHz can be selected. For MCLK equal to 3.84MHz, sampling frequencies up to 60kHz can be selected.

The WOLA clock (WCLK) feature allows WOLA operations to be performed at a frequency slower than SYS_CLK. This feature allows

the dynamic current consumption related to the digital blocks to be “spread” over a longer period of time, smoothing the system’s

dynamic current draw, which can affect the audio signal.

相關PDF資料 |

PDF描述 |

|---|---|

| 0X860 | OSCILLOSCOPE 100MHz ANALOGUE |

| 2-5174339-5 | 68 CONTACT(S), MALE, STRAIGHT TELECOM AND DATACOM CONNECTOR, SOLDER |

| 2-5174339-4 | 50 CONTACT(S), MALE, STRAIGHT TELECOM AND DATACOM CONNECTOR, SOLDER |

| 2-640445-1 | 21 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, SOLDER |

| 208006-1 | 9 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR, SOLDER, PLUG |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 0W912 | 制造商:Intel 功能描述:MBRD, SUPERMANIII, DELL |

| 0W9495 | 功能描述:電纜組件 DC POWER cbl RoHS:否 制造商:Molex 產(chǎn)品:Power Assemblies 類型:Cable Assembly 連接器端口 A:No Connector 連接器端口 A 管腳計數(shù):4 連接器端口 B:No Connector 連接器端口 B 管腳計數(shù): 型式:Male 線規(guī) - 美國線規(guī)(AWG):20, 28 長度:0.305 m 顏色:Black, Red |

| 0WCGA-002-XTP | 制造商:AppliedMicro 功能描述: |

| 0WCHY117 | 制造商:The Cherry Corporation 功能描述: |

| 0WCHY403 | 制造商:The Cherry Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。