- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1977 > XRT82L24AIV-F (Exar Corporation)IC LIU E1 QAUD 100TQFP PDF資料下載

參數(shù)資料

| 型號: | XRT82L24AIV-F |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 37/39頁 |

| 文件大小: | 0K |

| 描述: | IC LIU E1 QAUD 100TQFP |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 類型: | 線路接口裝置(LIU) |

| 驅(qū)動器/接收器數(shù): | 4/4 |

| 規(guī)程: | E1 |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-LQFP |

| 供應(yīng)商設(shè)備封裝: | 100-TQFP(14x14) |

| 包裝: | 托盤 |

| 其它名稱: | XRT82L24AIV-F-ND |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁

á

XRT82L24A

QUAD E1 LINE TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

REV. 1.1.2

5

21

55

71

TxClk_0

TxClk_1

TxClk_2

TxClk_3

I

Transmitter_n Clock Input: E1 rate at 2.048MHz ± 50ppm.

During normal operation both in Host Mode and Hardware Mode, TxClk is used

for sampling input data at TxPOS/TData and TxNEG, while MCLK is used as

the timing reference for the transmit pulse shaping circuit. If TxClk is active

while MClk is not present, TxPOS and TxNEG accepts NRZ data input and the

transmit pulse width is determined by TxClk clock duty cycle. If TxClk is tied to

“Low”, TxPOS and TxNEG input accepts RZ data format and the pulse width is

determined by the duty cycle of the input data. In RZ Mode, single-rail data for-

mat is not supported.

In Hardware Mode, if TxClk is tied "High" for more than 10 s, then TAOS (a

continuous all one's AMI signal) will be transmitted to the line using MCLK as

timing reference.

If TxClk_0 is tied “Low” for more than 10 s, the transmitter will be powered

down and the output will be tri-stated.

14

15

16

17

TxOFF_0

TxOFF_1

TxOFF_2

TxOFF_3

I

Powered-down Transmitter_n:

In Hardware Mode, tie this pin "High" to power-down channel 0 transmitter and

set TTIP_n and TRing_n to high impedance.

NOTE: Internally pulled -up with a 50k

resistor.

91

35

41

85

TRing_0

TRing_1

TRing_2

TRing_3

O

Transmitter_n Ring Output:

Negative Differential data output to the line.

89

37

39

87

TTIP_0

TTIP_1

TTIP_2

TTIP_3

O

Transmitter_n Tip Output:

Positive Differential data output to the line.

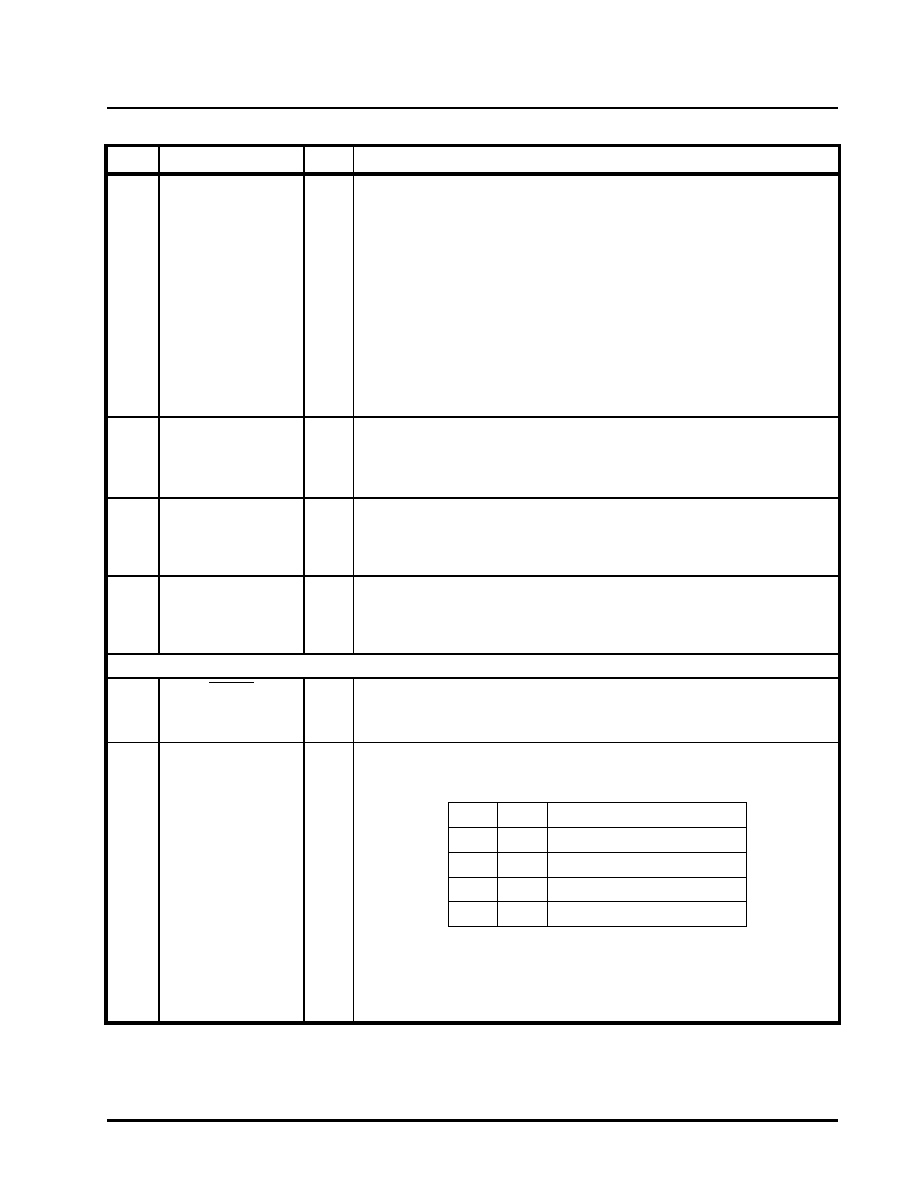

MICROPROCESSOR INTERFACE

6

RESET

I

Hardware Reset (Active Low). When this pin is tied Low for more than 10

S,

the device is put in the reset state.

NOTE: Internally pulled -up with a 50k

resistor.

7

PTS1

ClkE

I

Processor Type Select bit 1:

Host Mode

In Host Mode the appropriate bits are set in the command mode

Hardware Mode:

The state of the ClkE input controls the sampling edge of both TxClk and RxClk.

A “1” selects the positive edge of TxClk and RxClk

A “0” selects the negative edge of TxClk and RxClk.

PIN DESCRIPTIONS

PIN #NAME

TYPE

DESCRIPTION

8HC11,8081,80C188 (async.)

Motorola 68K (async.)

Intel x86 (sync.)

Intel i906,Motorola 860 (sync.)

PTS1

0

1

0

1

PTS2

0

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT83D10IW | IC LIU T1/E1 SGL 28SOJ |

| XRT83L30IV-F | IC LIU LH/SH T1/E1 SGL 64TQFP |

| XRT83L314IB-L | IC LIU T1/E1/J1 14CH 304TBGA |

| XRT83L34IV-F | IC LIU T1/E1/J1 QUAD 128TQFP |

| XRT83L38IB-F | IC LIU T1/E1/J1 OCTAL 225BGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT82L24ES | 功能描述:界面開發(fā)工具 Evaluation Board for XRT82L24 Series RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XRT82L24IV | 制造商:EXAR 制造商全稱:EXAR 功能描述:QUAD E1 LINE TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR |

| XRT82L34IV | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Interface IC |

| XRT83D10 | 制造商:EXAR 制造商全稱:EXAR 功能描述:SINGLE CHANNEL DS1/CEPT LINE INTERFACE UNIT |

| XRT83D10ES | 功能描述:外圍驅(qū)動器與原件 - PCI 1 CHT1/E1LIUSH RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。