- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383961 > TMX320DM6443AZWT (Texas Instruments, Inc.) Digital Media System-on-Chip PDF資料下載

參數(shù)資料

| 型號: | TMX320DM6443AZWT |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Digital Media System-on-Chip |

| 中文描述: | 數(shù)字媒體系統(tǒng)片上 |

| 文件頁數(shù): | 100/221頁 |

| 文件大小: | 1582K |

| 代理商: | TMX320DM6443AZWT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁當前第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁

www.ti.com

3

4

1

RESET

Boot

Configuration Pins

2

10

11

5

DDR2 Low Group

(A)

DDR2 Z Group

(A)

12

6

DDR2 High Group

(A)

16

20

21

17

DDR2 Low/High Group

(A)

DDR2 Z/High Group

(A)

A.

DDR2 Z Group:

DDR_DQS[3:0], DDR_D[12:0]

DDR2 Low Group:

DDR_CLK0, DDR_CKE, DDR_A[12:0]

DDR2 High Group:

DDR_CLK0, DDR_CS, DDR_WE, DDR_RAS, DDR_CAS

DDR2 Z/High Group:

DDR_DQM[3:0],

DDR2 Low/High Group:

DDR_BS[2:0]

Low Group:

DMARQ/UART_RXD1, VCLK, RTCK, TDO, VPBECLK, YOUT0/G5/AEAW0, YOUT1/G6/AEAW1,

YOUT2/G7/AEAW2, YOUT3/R3/AEAW3, YOUT4/R4/AEAW4, COUT3/B6/DSP_BT, COUT2/B5/EM_WIDTH,

COUT1/B4/BTSEL1, COUT0/B3/BTSEL0, TRST

High Group:

DMACK/UART_TXD1, EM_A[2]/(CLE), EM_A[1]/(ALE), EM_CS3, EM_WE/(WE)(IOWR)/DIOW

Z Group:

All other pins not listed above, with the exception of power and ground pins.

The following Z Group pins have an internal pullup (IPU):

DMARQ/UART_RXD1, VPBECLK, HSYNC, VSYNC,

YOUT0/G5/AEAW0, YOUT1/G6/AEAW1, YOUT2/G7/AEAW2, YOUT3/R3/AEAW3, YOUT4/R4/AEAW4,

COUT3/B6/DSP_BT COUT2/B5/EM_WIDTH, COUT1/B4/BTSEL1, COUT0/B3/BTSEL0, TRST, YI/CCD[7:0],

CI[3:0]/CCD[11:8], CI4/CCD12/UART_RTS2, CI5/CCD13/UART_CTS2, CI6/CCD14/UART_TXD2,

CI7/CCD15/UART_RXD2

The following Z Group pins have an internal pulldown (IPD): EM_WAIT/IORDY, TCK, TDI, TMS, EMU[1:0]

High/Low Group:

EM_BA[0]/DA0, EM_CS2, EM_OE/(RE)/(IORD)/DIOR

Low/High Group:

EM_R/W/INTRQ

Z/Invalid Group:

EM_D[15:0]

7

14

8

Low Group

(A)

Z Group

(A)

15

9

High Group

(A)

13

22

18

High/Low Group

(A)

23

19

Low/High Group

(A)

24

Z/Invalid Group

(A)

25

TMS320DM6443

Digital Media System-on-Chip

SPRS282E–DECEMBER 2005–REVISED MARCH 2007

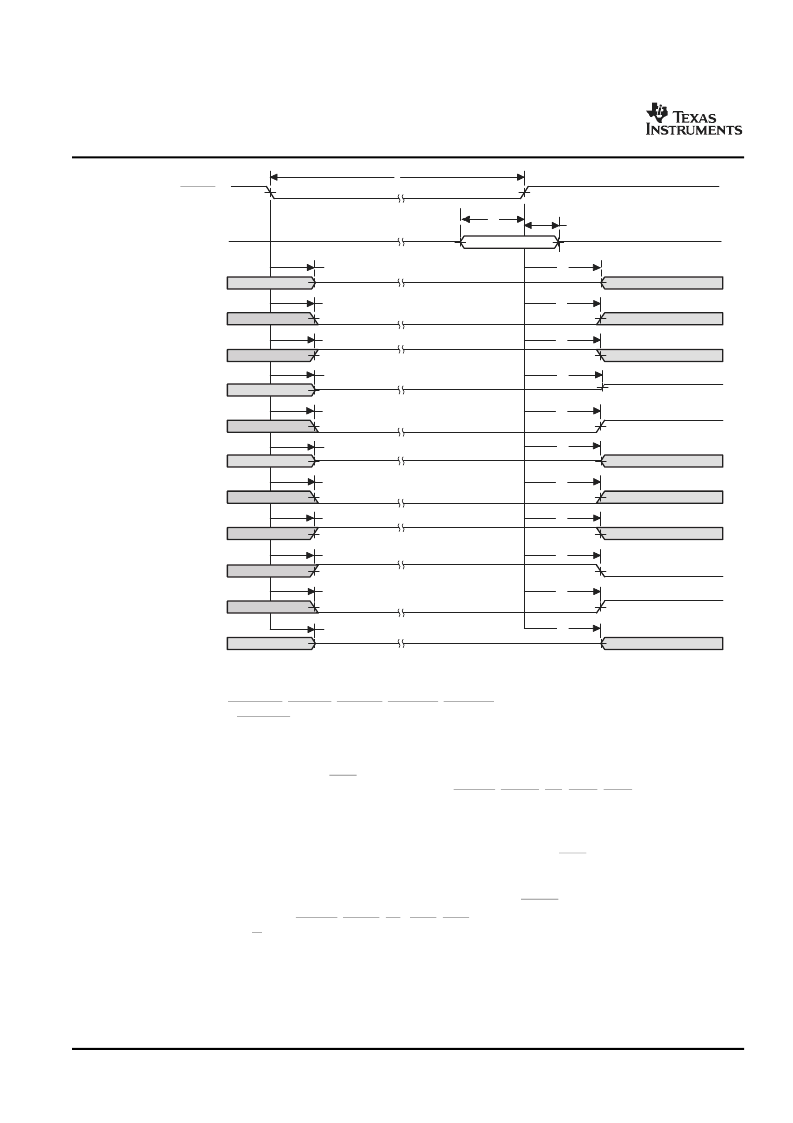

Figure 6-9. Reset Timing

100

Peripheral and Electrical Specifications

Submit Documentation Feedback

相關PDF資料 |

PDF描述 |

|---|---|

| TMX320DM6443ZWT | Digital Media System-on-Chip |

| TMS320DM647_08 | Digital Media Processor |

| TMS320DM647ZUT720 | Digital Media Processor |

| TMS320DM647ZUT900 | Digital Media Processor |

| TMS320DM648ZUT720 | Digital Media Processor |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TMX320DM6443BZWT | 制造商:Texas Instruments 功能描述: |

| TMX320DM6443CZWT | 制造商:Texas Instruments 功能描述: |

| TMX320DM6443ZWT | 制造商:Texas Instruments 功能描述: |

| TMX320DM6444AZWT | 制造商:Texas Instruments 功能描述:TMS320DM6443, TMS320DM6444 DIGITAL MEDIA SOC DATA SHEET - Trays |

| TMX320DM6446AZWT | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。