- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383838 > ST20GP1 MAX 7000 CPLD 256 MC 208-PQFP PDF資料下載

參數(shù)資料

| 型號(hào): | ST20GP1 |

| 英文描述: | MAX 7000 CPLD 256 MC 208-PQFP |

| 中文描述: | GPS處理器 |

| 文件頁(yè)數(shù): | 23/116頁(yè) |

| 文件大小: | 1107K |

| 代理商: | ST20GP1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)當(dāng)前第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)

ST20-GP1

23/116

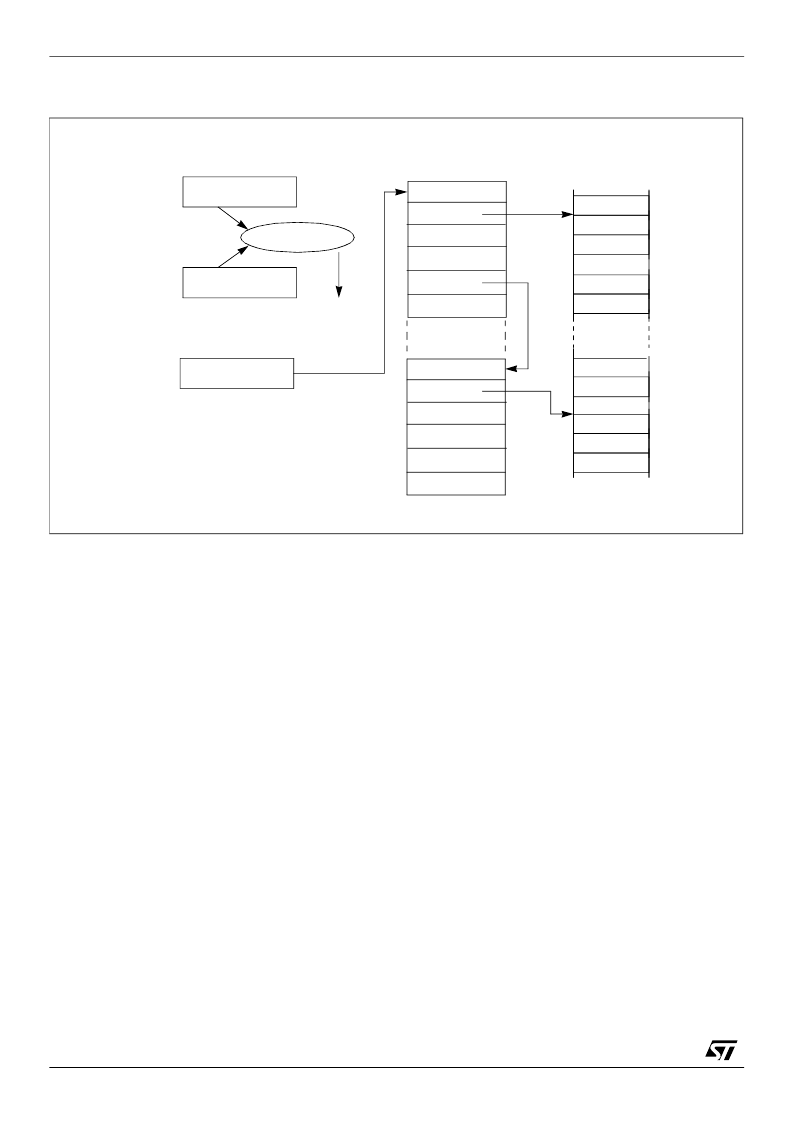

Figure 4.3 Timer registers

4.6

Traps and exceptions

A software error, such as arithmetic overflow or array bounds violation, can cause an error flag to

be set in the CPU. The flag is directly connected to the

ErrorOut

pin. Both the flag and the pin can

be ignored, or the CPU stopped. Stopping the CPU on an error means that the error cannot cause

further corruption. As well as containing the error in this way it is possible to determine the state of

the CPU and its memory at the time the error occurred. This is particularly useful for postmortem

debugging where the debugger can be used to examine the state and history of the processor

leading up to and causing the error condition.

In addition, if a trap handler process is installed, a variety of traps/exceptions can be trapped and

handled by software. A user supplied trap handler routine can be provided for each high/low

process priority level. The handler is started when a trap occurs and is given the reason for the

trap. The trap handler is not re-entrant and must not cause a trap itself within the same group. All

traps are individually maskable.

4.6.1

The trap mechanism is arranged on a per priority basis. For each priority there is a handler for each

group of traps, as shown in Figure 4.4.

Trap groups

ClockReg0

TnextReg0

TptrReg0

Workspaces

Program

5

21

31

Empty

comparator

Alarm

21

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST20GP6 | MAX 7000 CPLD 256 MC 208-RQFP |

| ST25C02AB1 | IC FLEX 6000 FPGA 16K 144-TQFP |

| ST25C02AB6 | Stratix FPGA 25K FBGA-672 |

| ST25C02AM1 | IC ACEX 1K FPGA 100K 208-PQFP |

| ST25C02AM6 | Cyclone II FPGA 20K FBGA-256 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST20-GP1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:GPS PROCESSOR |

| ST20GP1X33S | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:GPS PROCESSOR |

| ST20GP6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:GPS PROCESSOR |

| ST20-GP6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:GPS PROCESSOR |

| ST20GP6CT33S | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:GPS PROCESSOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。