- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98083 > SME1430LGA-480 64-BIT, 480 MHz, RISC PROCESSOR, CBGA587 PDF資料下載

參數(shù)資料

| 型號: | SME1430LGA-480 |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 64-BIT, 480 MHz, RISC PROCESSOR, CBGA587 |

| 封裝: | CERAMIC, LGA-587 |

| 文件頁數(shù): | 30/60頁 |

| 文件大小: | 646K |

| 代理商: | SME1430LGA-480 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當(dāng)前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

36

SME1430LGA-360

SME1430LGA-440

SME1430LGA-480

Highly Integrated 64-Bit RISC; L2-Cache, DRAM, PCI Interfaces

UltraSPARC-IIi CPU

May 1999

Sun Microsystems, Inc

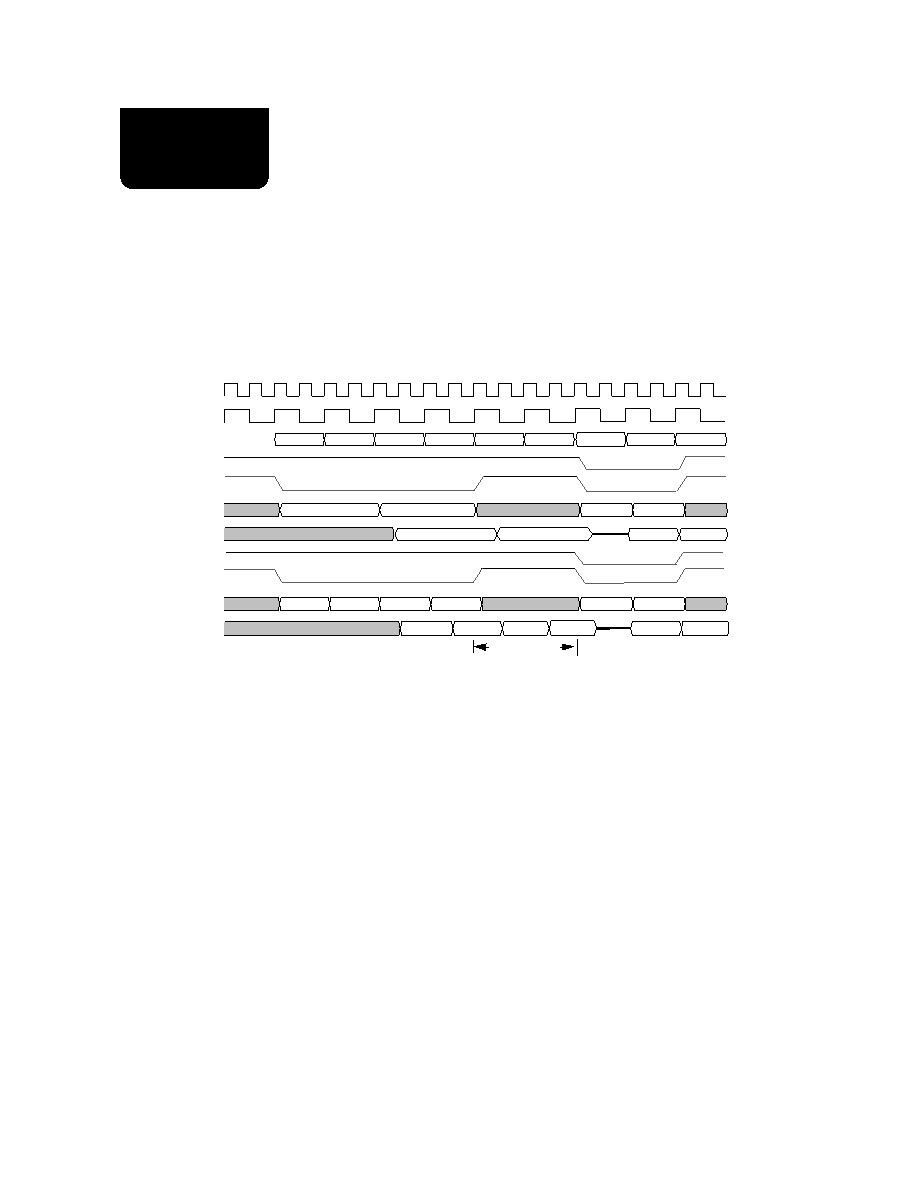

L2-cache Read Followed by L2-cache Write In 2-2-2 Mode

Figure 17 shows the two-cycle read-to-write turnaround penalty for 2-2-2 mode. The gure shows two reads

followed by two writes and two tag updates. The data for the second read (R1) is available in clock cycles 4

and 5. The UltraSPARC-IIi CPU cannot assert the write address in clock cycle 5 because electrical consider-

ations force an extra dead cycle while the L2-cache data bus driver is switched from the SRAMs to the

UltraSPARC-IIi CPU. The address for the rst write is asserted in clock cycle 6. This causes a two-cycle turn-

around penalty. The two-cycle penalty applies to both tag accesses and data accesses because there are two

stalled cycles between A1_tag and A2_tag, as well as between A1_data and A2_data.

Figure 17. Read -to-Write Turnaround Penalty (2-2-2 Mode Only) for L2-cache Read Hit (2-2-2 mode)

SRAM CYCLE

012345

TSYN_WR_L

R0

R1

TOE_L

ECAT

A0_tag

A1_tag

TDATA

D0_tag

DSYN_WR_L

DOE_L

ECAD

A0_data1 A0_data2 A1_data1

EDATA

CPU CLK

SRAM CLK

6

7

8

R1

D1_tag

D2_tag

A1_data2

R0

R1

R0

R1

W2

W3

W2

R0

R1

W3

W2

W3

A2_tag

A3_tag

D3_tag

A3_data

A2_data

D0_data1

D0_data2

D1_data1 D1_data2

D2_data D3_data

2 cycle penalty

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SME1701-BGA133 | 32-BIT, 133 MHz, MICROPROCESSOR, PBGA316 |

| SME5224AUPA-360 | 64-BIT, 360 MHz, RISC PROCESSOR |

| SME5410MCZ-270 | 64-BIT, 270 MHz, RISC PROCESSOR, XMA |

| SME5434PCI-440 | 64-BIT, 440 MHz, RISC PROCESSOR, XMA |

| SME5434PCI-480 | 64-BIT, 480 MHz, RISC PROCESSOR, XMA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SME14P95J4173 | 制造商:LIT 功能描述:Connector |

| SME160T1R0H | 制造商:Russell 功能描述: |

| SME160T221M22X40LL | 制造商:United Chemi-Con Inc 功能描述: |

| SME160T2R2H | 制造商:Russell 功能描述: |

| SME160VB10RM10X16FT | 制造商:United Chemi-Con Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。