- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄385814 > SAA7712 (NXP Semiconductors N.V.) Sound effects DSP PDF資料下載

參數(shù)資料

| 型號(hào): | SAA7712 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Sound effects DSP |

| 中文描述: | DSP的音效 |

| 文件頁(yè)數(shù): | 21/44頁(yè) |

| 文件大小: | 178K |

| 代理商: | SAA7712 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)

1999 Aug 05

21

Philips Semiconductors

Preliminary specification

Sound effects DSP

SAA7712H

8.6

I

2

C-bus control

8.6.1

I

NTRODUCTION

A general description of the I

2

C-bus format can be

obtained from Philips Semiconductors, International

Marketing and Sales Communications (IMSC).

For the external control of the SAA7712H a fast I

2

C-bus

is implemented. This is a 400 kHz bus which is downward

compatible with the standard 100 kHz bus.

There are different types of control instructions:

Instructions to control the DSP program, program the

coefficient RAM and read the values of parameters

Instructions to control the equalizer, program the

equalizer coefficient RAM to be able to change the

centre frequency, gain and Q-factor of the equalizer

sections

Instructions to control the source selection and

programmable parts, e.g. PLL clock speed.

The detailed description of the I

2

C-bus and commands is

given in the following sections. The description of the

different bits in the memory map is given in Section 9.6.

The equalizer cannot be used and cannot be

programmed if there is no word select and bit clock signal

present on a selected digital source input; see

audio_source bit in Table 3 (I

2

S_IN1 and I

2

S_IN2).

The minimum limit of the audio sample frequency is

determined by

1

18

f

SCL

.

8.6.2

C

HARACTERISTICS OF THE

I

2

C-

BUS

The I

2

C-bus is for 2-way, 2-line communication between

different ICs or modules. The two lines are a serial data

line (SDA) and a serial clock line (SCL). Both lines must

be connected to V

DD

via a pull-up resistor when

connected to the output stages of a microcontroller. For a

400 kHz I

2

C-bus the recommendation from Philips

Semiconductors must be followed (e.g. up to loads of

200 pFonthebusapull-upresistorcanbeused,between

200 to 400 pF a current source or switched resistor must

be used). Data transfer can only be initiated when the bus

is not busy.

8.6.3

B

IT TRANSFER

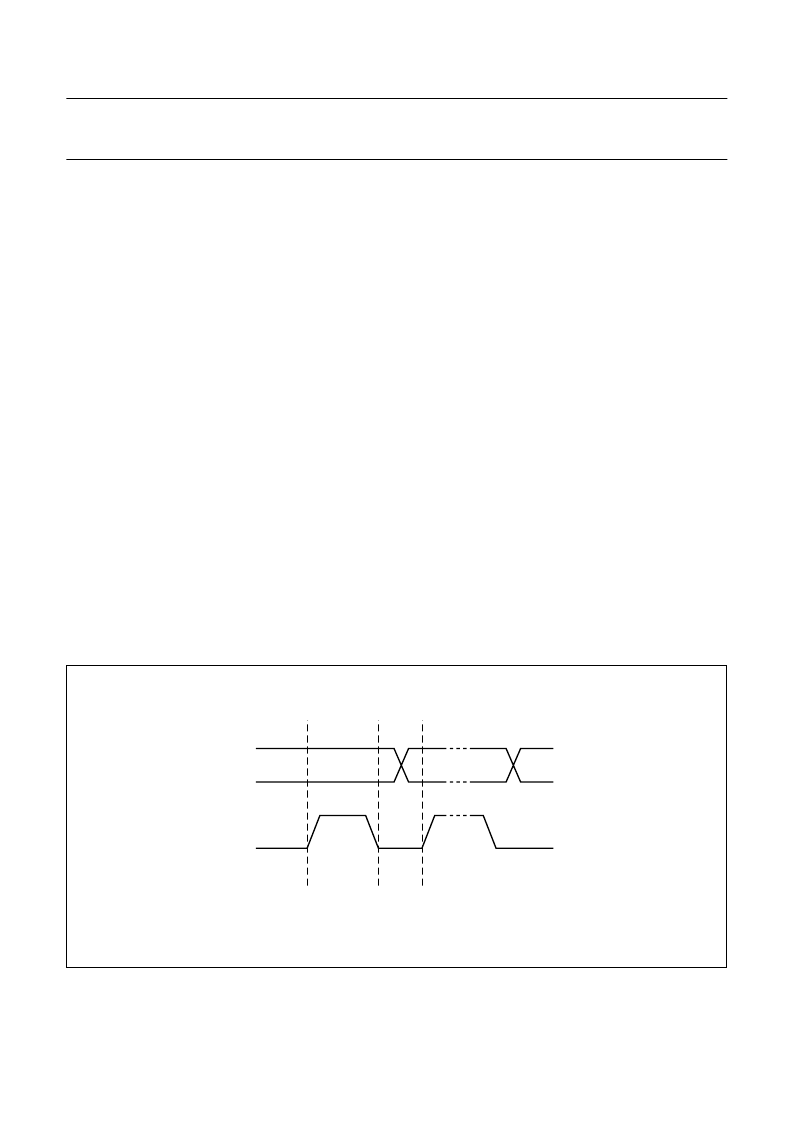

One data bit is transferred during each clock pulse.

The data on the SDA line must remain stable during the

HIGH period of the clock pulse as changes in the data line

at this time will be interpreted as control signals

(see Fig.11). The maximum clock frequency is 400 kHz.

To be able to run on this high frequency all the inputs and

outputs connected to this bus must be designed for this

high speed I

2

C-bus according to the Philips specification.

Fig.11 Bit transfer on the I

2

C-bus.

handbook, full pagewidth

MGS216

SDA

SCL

data line

stable;

data valid

change

of data

allowed

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA8110G | Digital Signal Processor (DSP) for cameras(應(yīng)用于照相中的數(shù)字信號(hào)處理器) |

| SAA8122A | Digital Still Camera Processor (ImagIC family)(數(shù)字靜態(tài)照相處理器) |

| SAA8122AEL | Digital Still Camera Processor ImagIC family |

| SAB-C504-2R24M | 8-Bit CMOS Microcontroller |

| SAB-C504-2R40M | 8-Bit CMOS Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7712H | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Sound effects DSP |

| SAA7715 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Digital Signal Processor |

| SAA7715H | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Digital Signal Processor |

| SAA7724H | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Car radio digital signal processor |

| SAA7740 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Digital Audio Processing IC DAPIC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。