- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄385814 > SAA7388GP (NXP SEMICONDUCTORS) Error correction and host interface IC for CD-ROM ELM PDF資料下載

參數(shù)資料

| 型號(hào): | SAA7388GP |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | Error correction and host interface IC for CD-ROM ELM |

| 中文描述: | 8-BIT, 50.4 MHz, MICROCONTROLLER, PQFP80 |

| 文件頁(yè)數(shù): | 25/60頁(yè) |

| 文件大小: | 226K |

| 代理商: | SAA7388GP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

1996 Apr 26

25

Philips Semiconductors

Preliminary specification

Error correction and host interface IC for

CD-ROM (ELM)

SAA7388

7.8

Sub-CPU interface

The sub-CPU interface is a 3-wire synchronous serial protocol. The interface uses three signals; SYN is used as a

synchronization signal, SDA is the bidirectional open-collector data signal and SCL is the bit clock.

The start of a command is signalled by a pulse on the SYN input. After this pulse an 8-bit address byte will be sent by

the sub-CPU. The format of this address byte is given in Table 24.

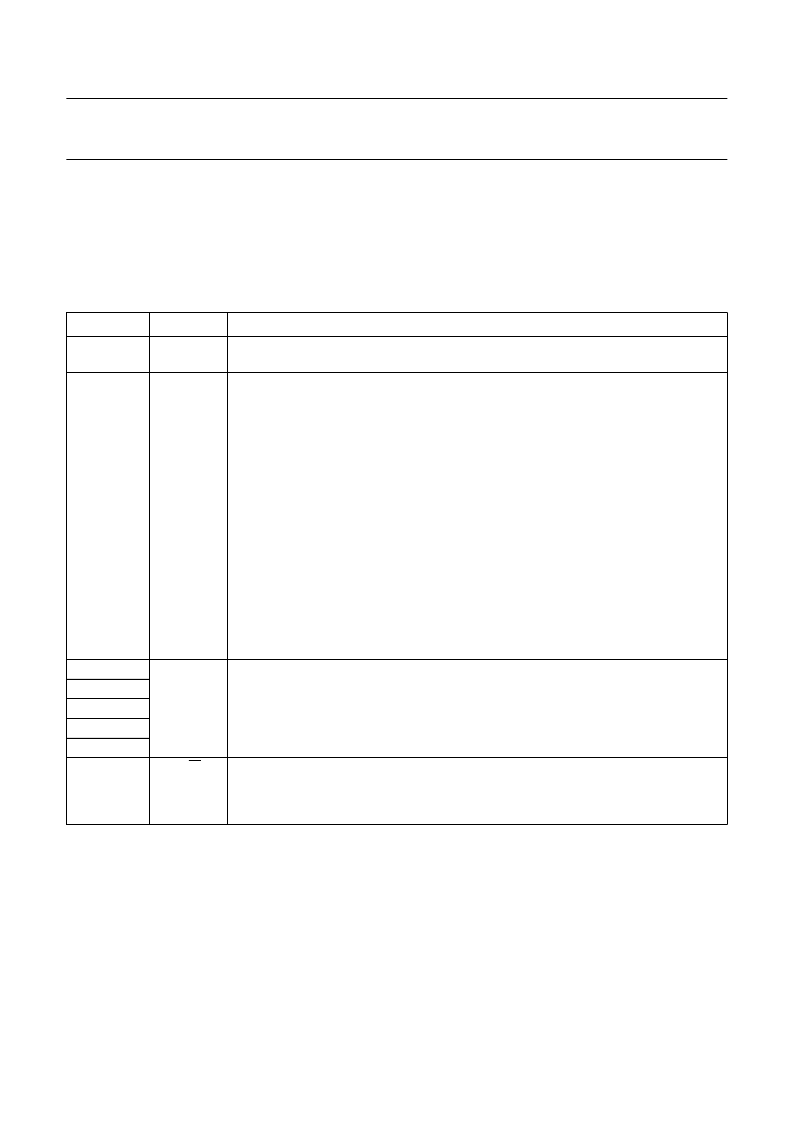

Table 24

Address byte format

BIT

NAME

DESCRIPTION

7

device

select

address

mode

If this bit is clear then the command will be for the SAA7388 otherwise the command is

for another device and the SAA7388 will not respond.

This bit controls the auto-increment function. After every byte has been read from or

written to the SAA7388 the address register is updated so that it is not necessary to

re-send the address to read or write the following byte. The way the address register is

updated is determined by the address mode bit. If the address mode bit is logic 0 then

the address register will increment by 1 if it is currently in the range 1 to 14 or 16 to 30. If

the address register is currently 15 or 31 then it will update to 0, if the address register is

at logic 0 then it will remain at address 0. If the address mode bit is logic 1 then the

address register will update in the following sequences;

6

Read: APCMD/COMIN -> APCMD/COMIN, IFSTAT -> DBCL -> DBCH -> HEAD0 ->

HEAD1 -> HEAD2 -> HEAD3 -> PTL -> PTH -> PTHH -> WAL -> WAH -> WAHH ->

STAT0 -> STAT1 -> STAT2 -> STAT3 -> APCMD/COMIN, ACMD -> ASMAT -> ADCTR

-> ADRSEL -> AINTR -> AFEAT -> APCMD/COMIN.

Write: ADATA/SBOUT -> ADATA/SBOUT, IFCTRL -> DBCL -> DBCH -> DACL ->

DACH -> DACHH -> DTRG -> DTACK -> WAL -> WAH -> WAHH -> CTRL0 -> CTRL1

-> PTL -> PTH -> PTHH -> SUB_L ->SUB_H -> 21 -> INCNF -> MEMS -> ASTAT ->

ITRG -> ADRADR -> ASAMT -> DTCTR -> ADRSEL -> AINTR -> AERR ->

ADATA/SBOUT.

This is the address that is loaded into the address register and determines which register

is accessed.

5

4

3

2

1

0

register

number

R/W

If this bit is set to logic 0 then the sub-CPU will send one or more data bytes after the

address byte. This data will be loaded into the specified registers. If this bit is set to

logic 1 then after sending the address byte the sub-CPU will clock out the contents of

one or more registers.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7388 | Error correction and host interface IC for CD-ROM ELM |

| SAA7392HL | Channel encoder/decoder CDR60 |

| SAA7392 | Channel encoder/decoder CDR60(通道編碼器/譯碼器) |

| SAA7705H | Car radio Digital Signal Processor(DSP)(車(chē)載電臺(tái)數(shù)字信號(hào)處理器) |

| SAA7712H | Sound effects DSP(聲音效應(yīng)數(shù)字信號(hào)處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7390 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:High performance Compact Disc-Recordable CD-R controller |

| SAA7390GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:High performance Compact Disc-Recordable CD-R controller |

| SAA7391 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ATAPI CD-R block encoder/decoder |

| SAA7391H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ATAPI CD-R block encoder/decoder |

| SAA7392 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Channel encoder/decoder CDR60 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。