- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45218 > MC68HC05C0B (MOTOROLA INC) 8-BIT, 4 MHz, MICROCONTROLLER, PDIP42 PDF資料下載

參數(shù)資料

| 型號(hào): | MC68HC05C0B |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 4 MHz, MICROCONTROLLER, PDIP42 |

| 封裝: | SDIP-42 |

| 文件頁(yè)數(shù): | 54/96頁(yè) |

| 文件大小: | 357K |

| 代理商: | MC68HC05C0B |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)當(dāng)前第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)

Section 10: Multi-Function Timer

MOTOROLA

Page 49

MC68HC05C0 Specification Rev. 1.2

selection) stage goes active. A CPU interrupt request will be generated if RTIE is set.

Clearing the RTIF is done by writing a ’1’ to RTIFC. Writing to RTIF has no effect. Reset

clears RTIF.

10.2.3

TOFE - Timer Over Flow Enable

When this bit is set, a CPU interrupt request is generated when the TOF bit is set. When

this bit is clear, the TOF flag is prevented from generating an interrupt request. A reset

clears this bit.

10.2.4

RTIE - Real Time Interrupt Enable

When this bit is set, a CPU interrupt request is generated when the RTIF bit is set. When

this bit is clear, the RTIF flag is prevented from generating an interrupt request. A reset

clears this bit.

10.2.5

TOFC - Timer Over Flow Flag Clear

TOF is cleared by writing a logic 1 to TOFC. Writing a logic 0 to TOFC has no effect on

TOF. This bit always reads as logic 0.

10.2.6

RTIFC - Real Time Interrupt Flag Clear

RTIF is cleared by writing a logic 1 to RTIFC. Writing a logic 0 to RTIFC has no effect on

RTIF. This bit always reads as logic 0.

10.2.7

RT1:RT0 - Real Time Interrupt Rate Select

These two bits select one of four taps from the Real Time Interrupt circuit. Table 10-1

shows the available interrupt rates with a variety of oscillator frequencies. A reset sets

these two bits which selects the lowest periodic rate and gives the maximum time in which

to alter these bits if necessary. Care should be taken when altering RT0 and RT1 if the time-

out period is imminent or uncertain. If the selected tap is modified during a cycle in which

the counter is switching, an RTIF could be missed or an additional one could be generated.

To avoid problems, the COP should be cleared before changing RTI taps.

The encoding for these two bits is shown below.

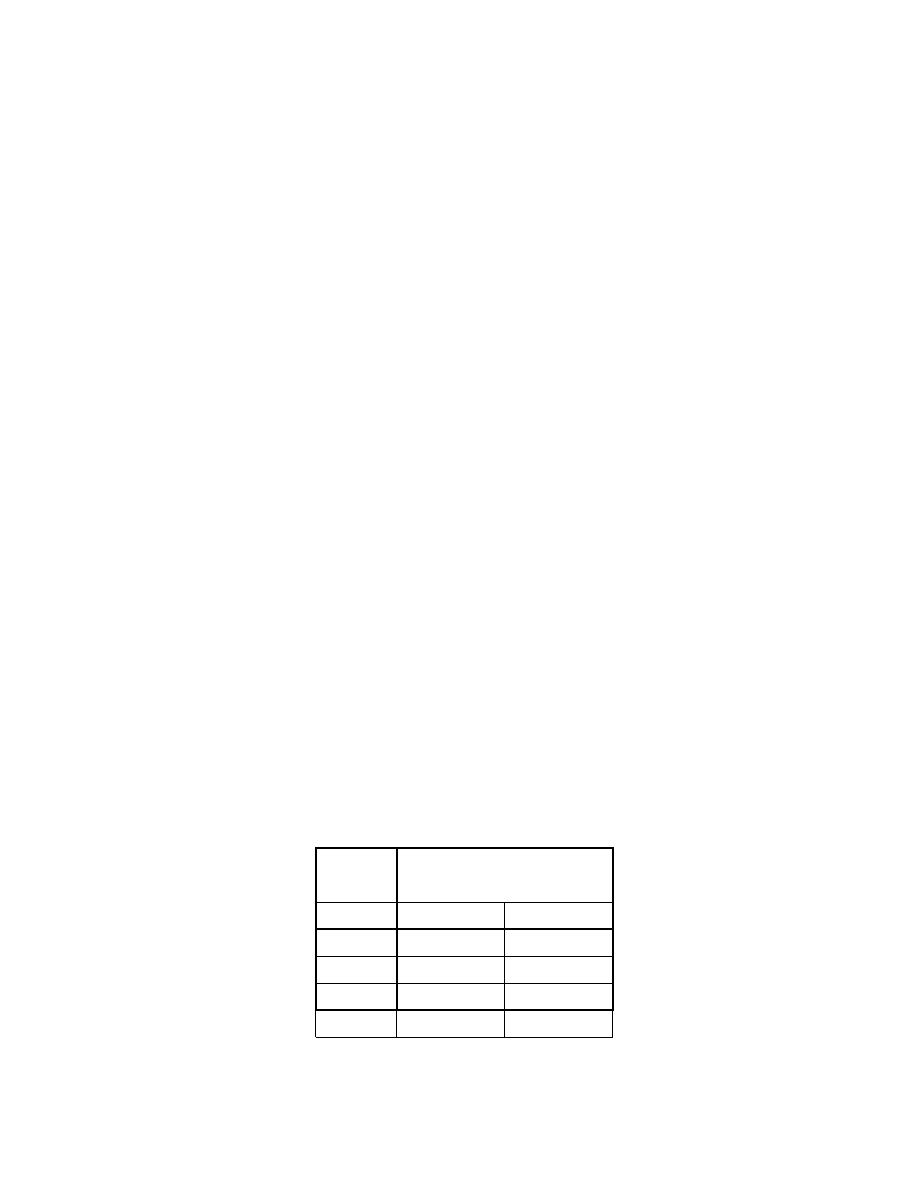

Table 10-1: RTI Rates

RT1:RT0

16.0 MHz

8.0 MHz

00

8.192 ms

16.384 ms

01

16.384 ms

32.768 ms

10

32.768 ms

65.536 ms

11

RTI RATES AT fosc

8.192 ms

4.096 ms

FREQUENCY SPECIFIED:

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC05C0P | 8-BIT, 4 MHz, MICROCONTROLLER, PDIP40 |

| MC68HC05C0FN | 8-BIT, 4 MHz, MICROCONTROLLER, PQCC44 |

| MC68HC05C12AFN | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PQCC44 |

| MC68HSC05C12AB | 8-BIT, MROM, 4.1 MHz, MICROCONTROLLER, PDIP42 |

| MC68HSC05C12ACP | 8-BIT, MROM, 4.1 MHz, MICROCONTROLLER, PDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC05C0CP | 制造商:Motorola Inc 功能描述: |

| MC68HC05C12 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCMOS MICROCONTROLLER UNITS |

| MC68HC05C12B | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCMOS MICROCONTROLLER UNITS |

| MC68HC05C12CP | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCMOS MICROCONTROLLER UNITS |

| MC68HC05C12P | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCMOS MICROCONTROLLER UNITS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。