- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4581 > IDT72T6360L6BB (IDT, Integrated Device Technology Inc)IC FLOW-CTRL 36BIT 6NS 324-BGA PDF資料下載

參數(shù)資料

| 型號: | IDT72T6360L6BB |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 10/51頁 |

| 文件大小: | 0K |

| 描述: | IC FLOW-CTRL 36BIT 6NS 324-BGA |

| 標準包裝: | 1 |

| 類型: | 連續(xù)流量控制 |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 324-BGA |

| 供應(yīng)商設(shè)備封裝: | 324-PBGA(19x19) |

| 包裝: | 托盤 |

| 其它名稱: | 72T6360L6BB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

18

IDT72T6360 2.5V, SEQUENTIAL FLOW-CONTROL DEVICE

x9, x18, x36 BIT WIDE CONFIGURATION

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

FEBRUARY 10, 2009

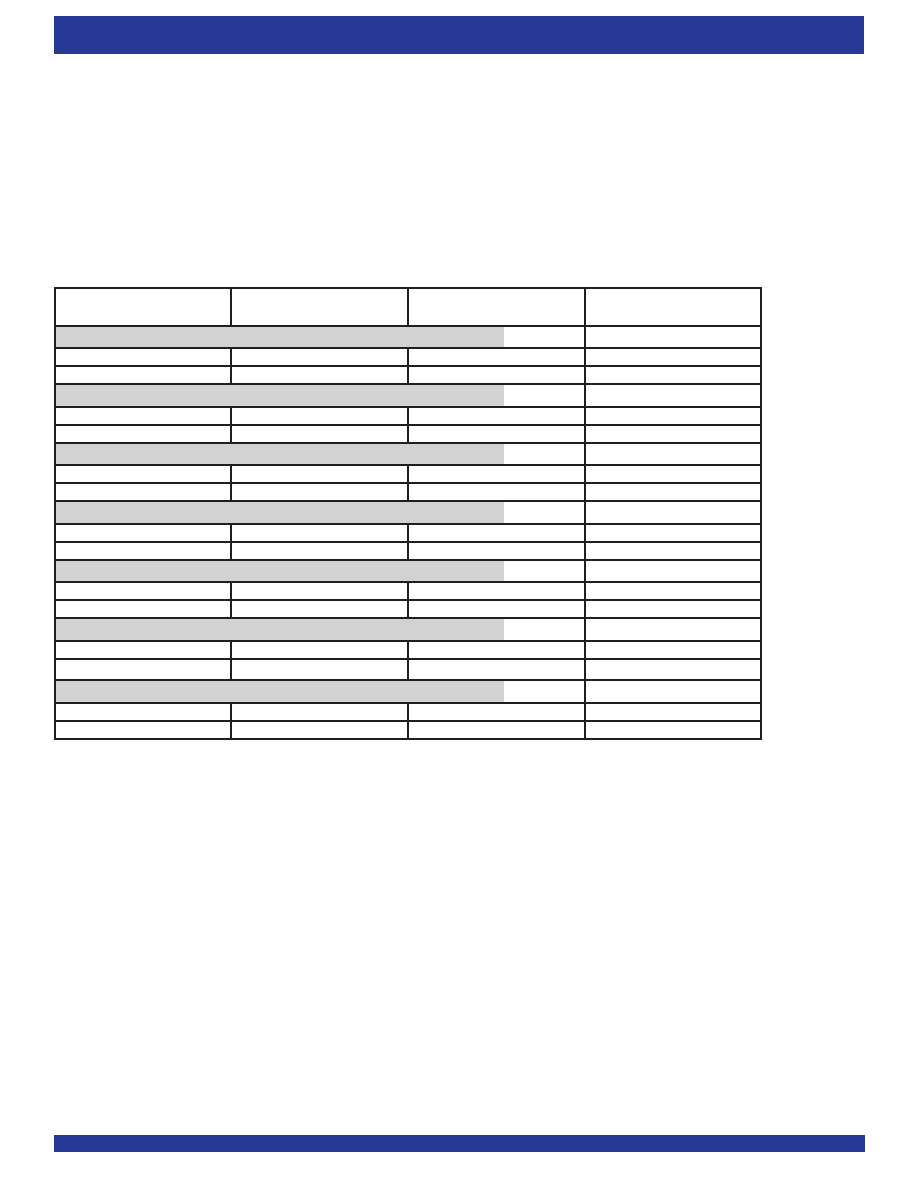

TOTAL AVAILABLE MEMORY USAGE

The sequential flow-control (SFC) is designed to efficiently use as much of

theDDRSDRAMmemoryaspossible,butduetothediscontinuitybetweenthe

SFC bus width (x36) and the DDR SDRAM interface (x16 or x32), some

columns in a row of the SDRAM will not be used. As a result, the total usable

memorywillbeslightlylessthanthetotalavailablememoryintheSDRAM.Table

5 outlines the total usable memory for the various configurations depending on

whether or not the Error Detection and Correction (EDC) feature is selected.

If the EDC feature is selected, 8 syndrome bits will be generated per every 64

bits of data. Therefore every third write burst to the SDRAM will send out the

8 syndrome bits, resulting in 24 unused bits inthe column. Therefore, using the

EDCfeature,therewillbesignificantlylessusablememoryofdatastorage.The

EDC function is described in the Error Detection and Correction section of this

datasheet.

Total DDR SDRAM

Total Usable

Density

Memory (EDC off)

Memory (EDC on)

Configuration 1

1 x [4Mb x 32]

128Mb

108Mb

72Mb

1 x [8Mb x 32]

256Mb

252Mb

144Mb

Configuration 2

1 x [8Mb x 16]

128Mb

108Mb

72Mb

1 x [16Mb x 16]

256Mb

216Mb

144Mb

Configuration 3

2 x [4Mb x 32]

256Mb

216Mb

144Mb

2 x [8Mb x 32]

512Mb

504Mb

288Mb

Configuration 4

2 x [4Mb x 32]

256Mb

122Mb

108Mb

2 x [8Mb x 32]

512Mb

284Mb

252Mb

Configuration 5

2 x [8Mb x 16]

256Mb

252Mb

144Mb

2 x [16Mb x 16]

512Mb

504Mb

288Mb

Configuration 6

3 x [8Mb x 16]

384Mb

284Mb

252Mb

3 x [16Mb x 16]

768Mb

567Mb

504Mb

Configuration 7

4 x [8Mb x 16]

512Mb

504Mb

288Mb

4 x [16Mb x 16]

1Gb

1008Mb

576Mb

TABLE 5 – TOTAL USEABLE MEMORY BASED ON VARIOUS CONFIGURATIONS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT77V500S25BCG8 | IC SW MEMORY 8X8 1.2BGPS 144-BGA |

| IDT77V500S25BC8 | IC SW MEMORY 8X8 1.2BGPS 144-BGA |

| LT1764AEFE-2.5#TRPBF | IC REG LDO 2.5V 3A 16TSSOP |

| LFXP10E-5F388C | IC FPGA 9.7KLUTS 244I/O 388-BGA |

| LFXP10E-4F388I | IC FPGA 9.7KLUTS 244I/O 388-BGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72T6360L6BBG | 功能描述:IC FLOW-CTRL 36BIT 6NS 324-BGA RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72T6360L7-5BB | 功能描述:IC FLOW-CTRL 48BIT 7-5NS 324-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72T6360L7-5BBI | 功能描述:IC FLOW-CTRL 48BIT 7-5NS 324-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72T6480L10BB | 功能描述:IC FLOW-CTRL 48BIT 10NS 324-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72T6480L10BBI | 功能描述:IC FLOW-CTRL 48BIT 10NS 324-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。