- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385407 > HT9480 (Holtek Semiconductor Inc.) Pager Controller PDF資料下載

參數(shù)資料

| 型號: | HT9480 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | Pager Controller |

| 中文描述: | 傳呼機控制器 |

| 文件頁數(shù): | 19/57頁 |

| 文件大小: | 1541K |

| 代理商: | HT9480 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

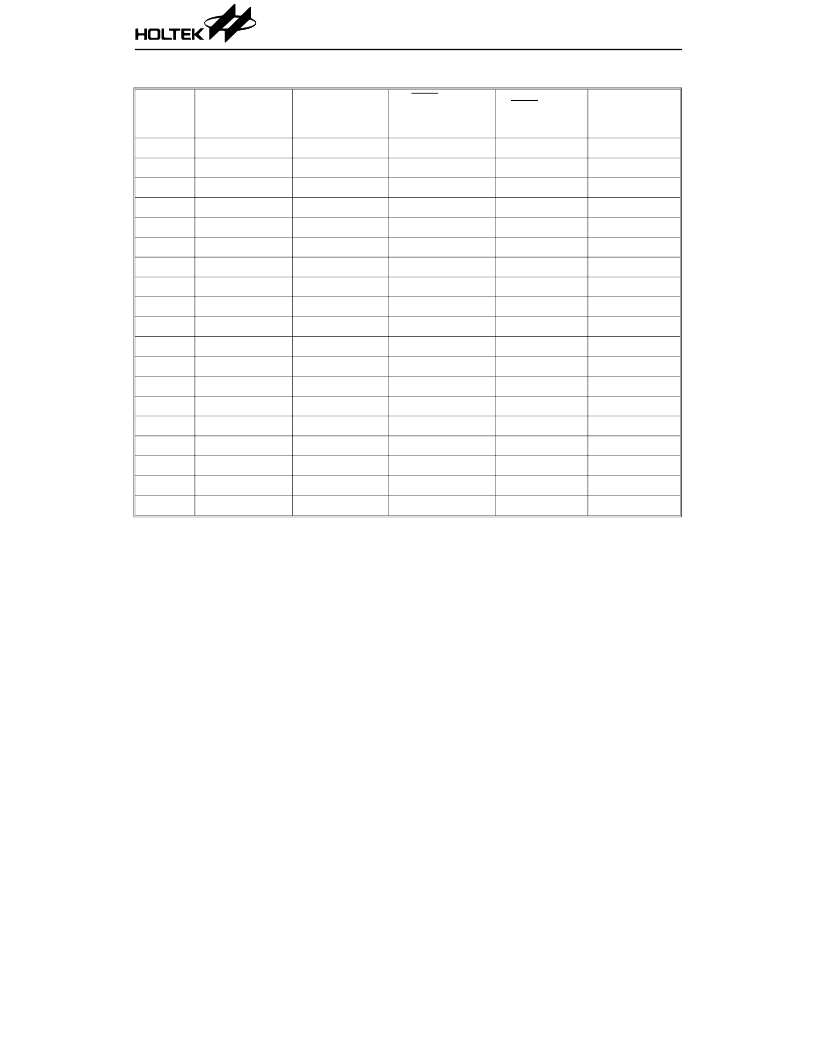

The states of the registers are summarized below.

R egister

Power-on

reset (POR )

WDT time-out

(normal

operation)

R E S reset

(normal

operation)

R E S reset

(HALT)

WDT time-

out (HALT )*

TMR0

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

TMRC0

00-0 1---

00-0 1---

00-0 1---

00-0 1---

uu-u u--

TMR1

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

TMRC1

00-0 1---

00-0 1---

00-0 1---

00-0 1---

uu-u u--

PC

0000H

0000H

0000H

0000H

0000H

MP0

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

MP1

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

ACC

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

TBLP

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

TBLH

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

STATUS

--00 xxxx

--1u uuuu

--uu uuuu

--01 uuuu

--11 uuuu

INTC

-000 0000

-000 0000

-000 0000

-000 0000

-uuu uuuu

WDTS

0000 0111

0000 0111

0000 0111

0000 0111

uuuu uuuu

PA

1111 1111

1111 1111

1111 1111

1111 1111

uuuu uuuu

PAC

1111 1111

1111 1111

1111 1111

1111 1111

uuuu uuuu

PB

1111 1111

1111 1111

1111 1111

1111 1111

uuuu uuuu

PBC

1111 1111

1111 1111

1111 1111

1111 1111

uuuu uuuu

PC

---- 1111

---- 1111

---- 1111

---- 1111

---- uuuu

PCC

---- 1111

---- 1111

---- 1111

---- 1111

---- uuuu

Note: “*” means “warm reset”

“u” means “unchanged”

“x” means “unknown”

T he measured result will remain in the

timer/event counter even when the activated

transient occurs again. In other words, only one

cycle measurement can be made until the TON

is set. The cycle measurement will re-function

as long as further transient pulses are received.

Note that, in this operation mode, the

timer/event counter starts counting not accord-

ing to the logic level but to the transient edges.

In the case of counting overflows, the counter is

re-loaded from its counter preload register and

issues an interrupt request, similar to the other

two modes.

To enable the counting operation, the value of

the timer on bit (TON; bit 4 of TMRC0 and

TMRC1) is “1”. In the pulse width measurement

mode, the TON is automatically cleared after

the measurement cycle is completed. In the

other two modes, namely the event count or

timer mode, the TON can be reset only by in-

structions. The overflow of the programmable

timer counter and of the timer/event counter

can be configured as one of the wake-up

sources. No matter what type of operation mode

is chosen, writing a 0 to E T0I and E T1I disables

the interrupt service of the programmable

timer counter and the timer/event counter, re-

spectively.

HT9480

19

23th Feb ’98

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT95168 | Caller ID Telephone IC |

| HT9580 | Character Pager Controller |

| HT95A30P | 8-Bit LCD Type Phone Controller MCU |

| HT95L300 | 8-Bit LCD Type Phone Controller MCU |

| HT95A20P | 8-Bit LCD Type Phone Controller MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT9480_02 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit Numerical Pager Controller MCU |

| HT94804 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Numeric Pager Controller ??(Simplified Chinese Version Only) |

| HT-95 | 制造商:FCI 功能描述:RATCHET CRIMP TOOL 制造商:FCI 功能描述:RATCHET CRIMP TOOL; Crimp Size:32AWG to 22AWG; For Use With:Crimp-to-Wire PV Receptacles & Pins ;RoHS Compliant: NA |

| HT95168 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Caller ID Telephone IC |

| HT9580 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Character Pager Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。