- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385399 > HT46C24 (Holtek Semiconductor Inc.) A/D Type 8-Bit MCU PDF資料下載

參數(shù)資料

| 型號: | HT46C24 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | A/D Type 8-Bit MCU |

| 中文描述: | 的A / D型8位微控制器 |

| 文件頁數(shù): | 11/49頁 |

| 文件大小: | 393K |

| 代理商: | HT46C24 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

HT46R24/HT46C24

Rev. 1.50

11

May 3, 2004

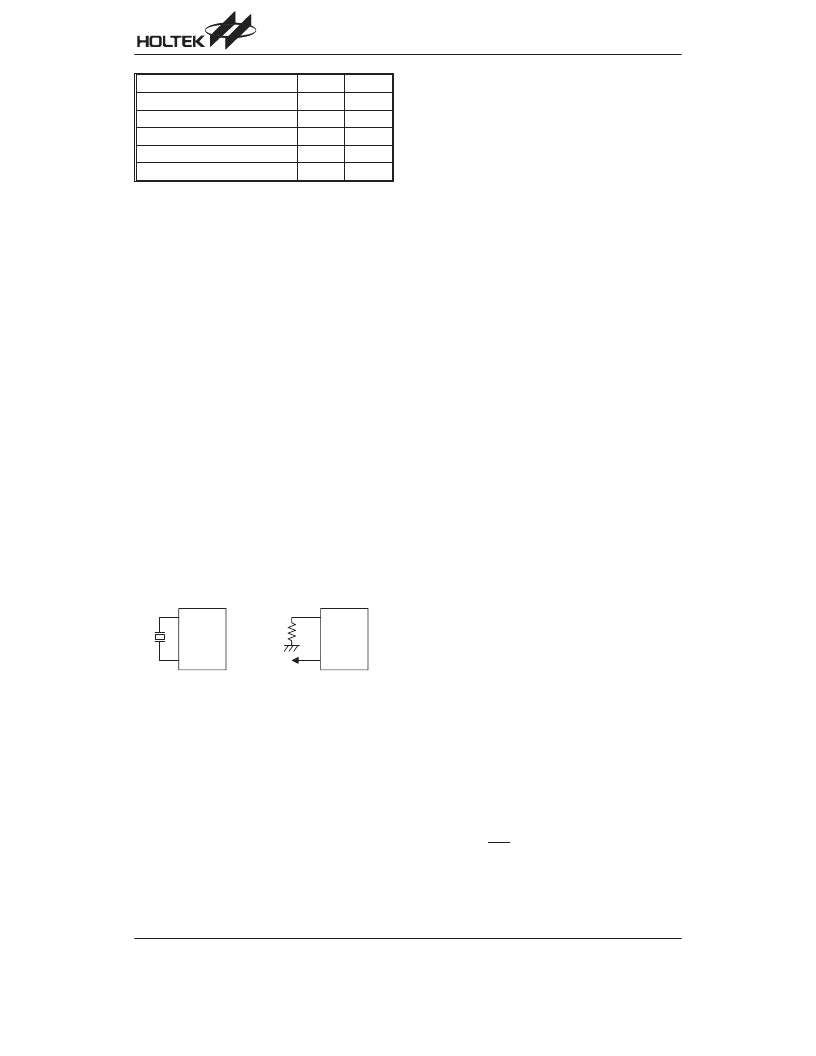

Interrupt Source

Priority

Vector

External Interrupt

1

04H

Timer/Event Counter 0 Overflow

2

08H

Timer/Event Counter 1 Overflow

3

0CH

A/D Converter Interrupt

I

2

C Bus Interrupt

4

10H

5

14H

TheTimer/EventCounter0/1interruptrequestflag(T0F,

T1F), external interrupt request flag (EIF), A/D converter

request flag (ADF), the I

2

C Bus interrupt request flag

(HIF), enable timer/event counter bit (ET0I, ET1I), en-

able external interrupt bit (EEI), enable A/D converter in-

terrupt bit (EADI), enable I

2

C Bus interrupt bit (EHI) and

enable master interrupt bit (EMI) constitute an interrupt

control register 0 (INTC0) and an interrupt control regis-

ter 1 (INTC1) which are located at 0BH and 1EH in the

data memory. EMI, EEI, ET0I, ET1I, EADI, EHI are used

to control the enabling/disabling of interrupts. These bits

prevent the requested interrupt from being serviced.

Once the interrupt request flags (T0F, T1F, EIF, ADF,

HIF) are set, they will remain in the INTC0 and INTC1

register until the interrupts are serviced or cleared by a

software instruction.

It is recommended that a program does not use the

CALL subroutine within the interrupt subroutine. In-

terrupts often occur in an unpredictable manner or

need to be serviced immediately in some applications.

If only one stack is left and enabling the interrupt is not

well controlled, the original control sequence will be dam-

aged once the CALL operates in the interrupt subrou-

tine.

Oscillator Configuration

There are two oscillator circuits in the microcontroller.

Both are designed for system clocks, namely the RC os-

cillator and the Crystal oscillator, which are determined

by the option. No matter what oscillator type is selected,

the signal provides the system clock. The HALT mode

stops the system oscillator and ignores an external sig-

nal to conserve power.

If an RC oscillator is used, an external resistor between

OSC1 and VSS is required and the resistance must

range from 30k

to 750k . The system clock, divided

by 4, is available on OSC2, which can be used to syn-

chronize external logic. The RC oscillator provides the

most cost effective solution. However, the frequency of

oscillation may vary with VDD, temperatures and the

chip itself due to process variations. It is, therefore, not

suitable for timing sensitive operations where an accu-

rate oscillator frequency is desired.

If the Crystal oscillator is used, a crystal across OSC1

and OSC2 is needed to provide the feedback and phase

shift required for the oscillator, and no other external

components are required. Instead of a crystal, a resona-

tor can also be connected between OSC1 and OSC2 to

get a frequency reference, but two external capacitors in

OSC1 and OSC2 are required (If the oscillating fre-

quency is less than 1MHz).

The WDT oscillator is a free running on-chip RC oscillator,

and no external components are required. Even if the sys-

tem enters the power down mode, the system clock is

stopped, but the WDT oscillator still works with a period of

approximately 65 s at 5V. The WDT oscillator can be dis-

abled by option to conserve power.

Watchdog Timer

WDT

The WDT clock source is implemented by a dedicated

RC oscillator (WDT oscillator) or instruction clock (sys-

tem clock divided by 4) decided by options. This timer is

designedtopreventasoftwaremalfunctionorsequence

jumping to an unknown location with unpredictable re-

sults. The watchdog timer can be disabled by a option. If

the watchdog timer is disabled, all the executions re-

lated to the WDT result in no operation.

Once an internal WDT oscillator (RC oscillator with pe-

riod 65 s at 5V normally) is selected, it is divided by

2

12

~2

15

(by option to get the WDT time-out period). The

WDT time-out minimum period is 300ms~600ms. This

time-out period may vary with temperature, VDD and

process variations. By selection from the WDT option,

longer time-out periods can be realized. If the WDT

time-out is selected 2

15

, the maximum time-out period is

divided by 2

15

~2

16

about 2.1s~4.3s.

If the WDT oscillator is disabled, the WDT clock may still

come from the instruction clock and operate in the same

manner except that in the HALTstate the WDTmay stop

counting and lose its protecting purpose. In this situation

the logic can only be restarted by external logic. If the

device operates in a noisy environment, using the

on-chip RC oscillator (WDT OSC) is strongly recom-

mended, since the HALT will stop the system clock.

The WDT overflow under normal operation will initialize

chip reset and set the status bit TO. Whereas in the

HALT mode, the overflow will initialize a warm reset

only the PC and SP are reset to zero. To clear the con-

tents of WDT, three methods are adopted; external reset

(a low level to RES), software instructions, or a HALT in-

struction. The software instructions include CLR WDT

and the other set CLR WDT1 and CLR WDT2. Of these

two types of instruction, only one can be active depend-

. *

. .

*

. .

*

*

$

,

' -

System Oscillator

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT46R24 | A/D Type 8-Bit MCU |

| HT46C46 | Cost-Effective A/D Type 8-Bit MCU |

| HT46C47 | Cost-Effective A/D Type 8-Bit MCU |

| HT46R46 | Cost-Effective A/D Type 8-Bit MCU |

| HT46C62 | A/D with LCD Type 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT46C46 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Cost-Effective A/D Type 8-Bit MCU |

| HT46C46E | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Cost-Effective A/D Type 8-Bit MCU |

| HT46C47 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Cost-Effective A/D Type 8-Bit MCU |

| HT46C47E | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Cost-Effective A/D Type 8-Bit MCU |

| HT46C48A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Cost-Effective A/D Type 8-Bit MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。