- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄2066 > AS3543-ECTP (ams)IC CODEC AUDIO FRONT END 68CTBGA PDF資料下載

參數(shù)資料

| 型號: | AS3543-ECTP |

| 廠商: | ams |

| 文件頁數(shù): | 70/92頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC CODEC AUDIO FRONT END 68CTBGA |

| 標準包裝: | 4,000 |

| 類型: | 音頻編解碼器 |

| 應(yīng)用: | 便攜式音頻,電話 |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 68-TFBGA |

| 供應(yīng)商設(shè)備封裝: | 68-CTBGA(6x6) |

| 包裝: | 帶卷 (TR) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁當前第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

www.austriamicrosystems.com

Revision 1.11

71 - 91

AS3543 3v2

Data Sheet - R e g i s t e r D e f i n i t i o n

3:2

DRIVE_XRES<1:0>

00

R/W

Sets the XRES output pin to open-drain, push-pull or tri-state

and sets various driving strengths

00: 6mA open-drain output

01: 6mA push-pull output

10: 1mA push-pull output

11: HiZ, stri-state

1:0

MUX_XRES<1:0>

00

R/W

Multiplexes various digital signals to the XRES output pin

00: XRES, active low reset signal

01: CLK32k, 32kHz RTC oszillator output

10: CLKINT1, internal clock signal, see Clk_Cntr regsiter

11: PWM, PMW_Cntr register

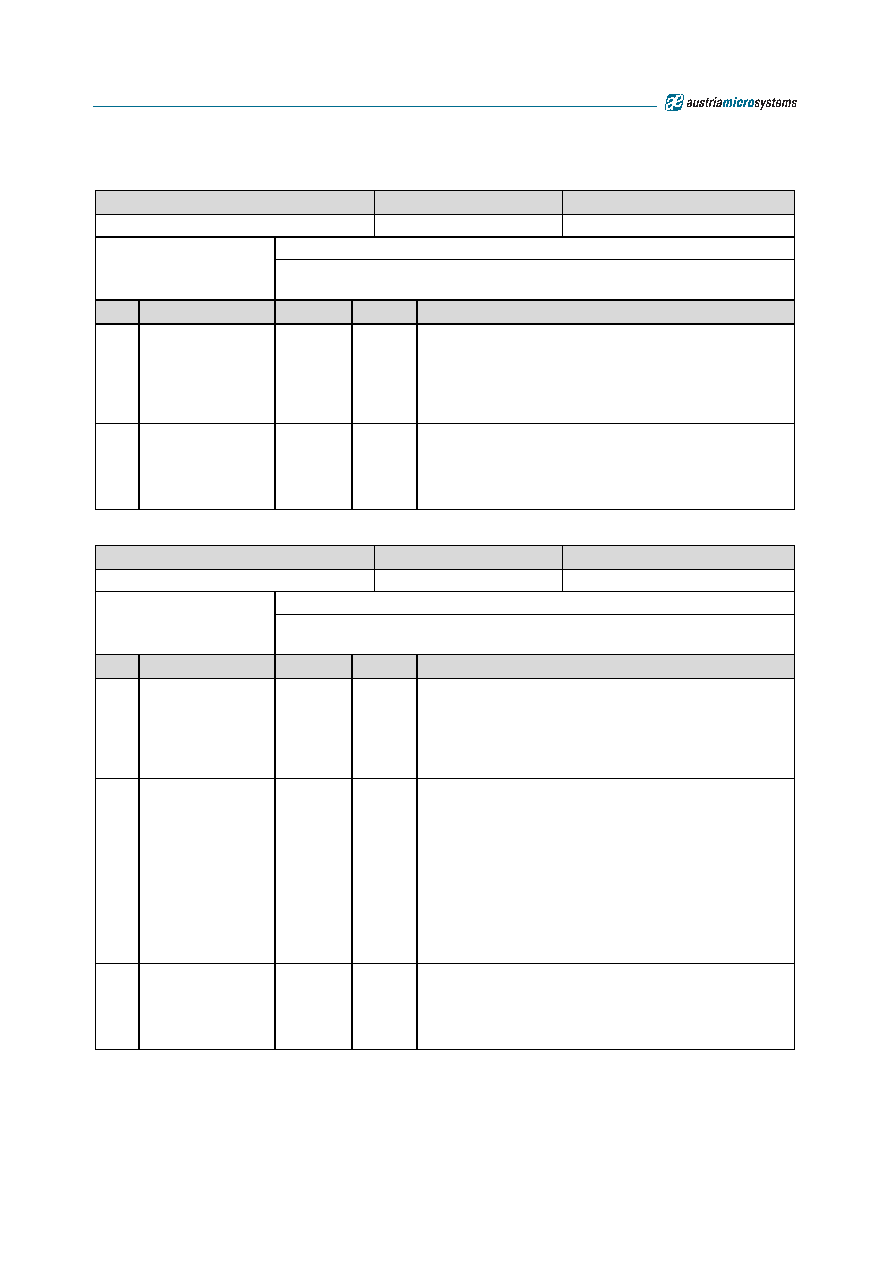

Table 69. Out_Cntr2 Register

Name

Base

Default

Out_Cntr2

2-wire serial

00h

Offset: 1Ah-2

Q24M and Q32k Output Control Register

This is an extended register and needs to be enabled by writing 010b to Reg. 1Ch first.

This register is reset at a AVDD27-POR.

Bit

Bit Name

Default

Access

Bit Description

7:6

DRIVE_Q24M<1:0>

00

R/W

Sets the PWGD output pin to push-pull or tri-state and sets

various driving strengths

00: 6mA push-pull output

01: HiZ, stri-state

10: 2mA push-pull output

11: 1mA push-pull output

5:4

MUX_Q24M<1:0>

00

R/W

Multiplexes various digital signals to the PWGD output pin

00: CLK24M, 24MHz oszillator output signal

01: CLKINT1, internal clock signal, see Clk_Cntr regsiter

10: CLKINT2, internal clock signal, see Clk_Cntr regsiter

11: PWM, PMW_Cntr register

3:2

DRIVE_Q32k<1:0>

00

R/W

Sets the XRES output pin to push-pull or tri-state and sets

various driving strengths

00: 6mA push-pull output

01: HiZ, stri-state

10: 2mA push-pull output

11: 1mA push-pull output

1:0

MUX_Q32k<1:0>

00

R/W

Multiplexes various digital signals to the XRES output pin

00: CLK32k, 32kHz RTC oszillator output signal

01: CLKINT1, internal clock signal, see Clk_Cntr regsiter

10: CLKINT2, internal clock signal, see Clk_Cntr regsiter

11: PWM, PMW_Cntr register

Table 68. Out_Cntr1 Register

Name

Base

Default

Out_Cntr1

2-wire serial

00h

Offset: 1Ah-1

PWGD and XRES Output Control Register

This is an extended register and needs to be enabled by writing 001b to Reg. 1Ch first.

This register is reset at a AVDD27-POR.

Bit

Bit Name

Default

Access

Bit Description

ams

AG

Technical

content

still

valid

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ASM2I9940LG-32LT | IC CLK BUFFER 2:18 250MHZ 32LQFP |

| ASM3P2780AF-06OR | IC FREQ MOD 4X EMI REDUCT 6TSOP |

| AT42QT1011-MAH | IC SENSR TOUCH/PROX 1CH 8-UDFN |

| AT42QT2161-MMU | IC TOUCH SENSOR 16KEY 28QFN |

| B300W35A102E1G | IC PROCESSOR AUDIO 24BIT WLCSP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AS35490FLF | 制造商:TT Electronics / IRC 功能描述:AS35490FLF |

| AS35490HLF | 制造商:TT Electronics / IRC 功能描述:AS35490HLF |

| AS35490JLF | 制造商:TT Electronics / IRC 功能描述:AS35490JLF |

| AS35491FLF | 制造商:TT Electronics / IRC 功能描述:AS35491FLF |

| AS35491HLF | 制造商:TT Electronics / IRC 功能描述:AS35491HLF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。