- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1894 > AD9824KCPZRL (Analog Devices Inc)IC CCD SIGNAL PROC 14BIT 48LFCSP PDF資料下載

參數(shù)資料

| 型號: | AD9824KCPZRL |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 20/24頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC CCD SIGNAL PROC 14BIT 48LFCSP |

| 標(biāo)準(zhǔn)包裝: | 2,500 |

| 類型: | CCD 信號處理器,14 位 |

| 輸入類型: | 邏輯 |

| 輸出類型: | 邏輯 |

| 接口: | 3 線串口 |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 48-VFQFN 裸露焊盤,CSP |

| 供應(yīng)商設(shè)備封裝: | 48-LFCSP-VQ(7x7) |

| 包裝: | 帶卷 (TR) |

REV. 0

AD9824

–5–

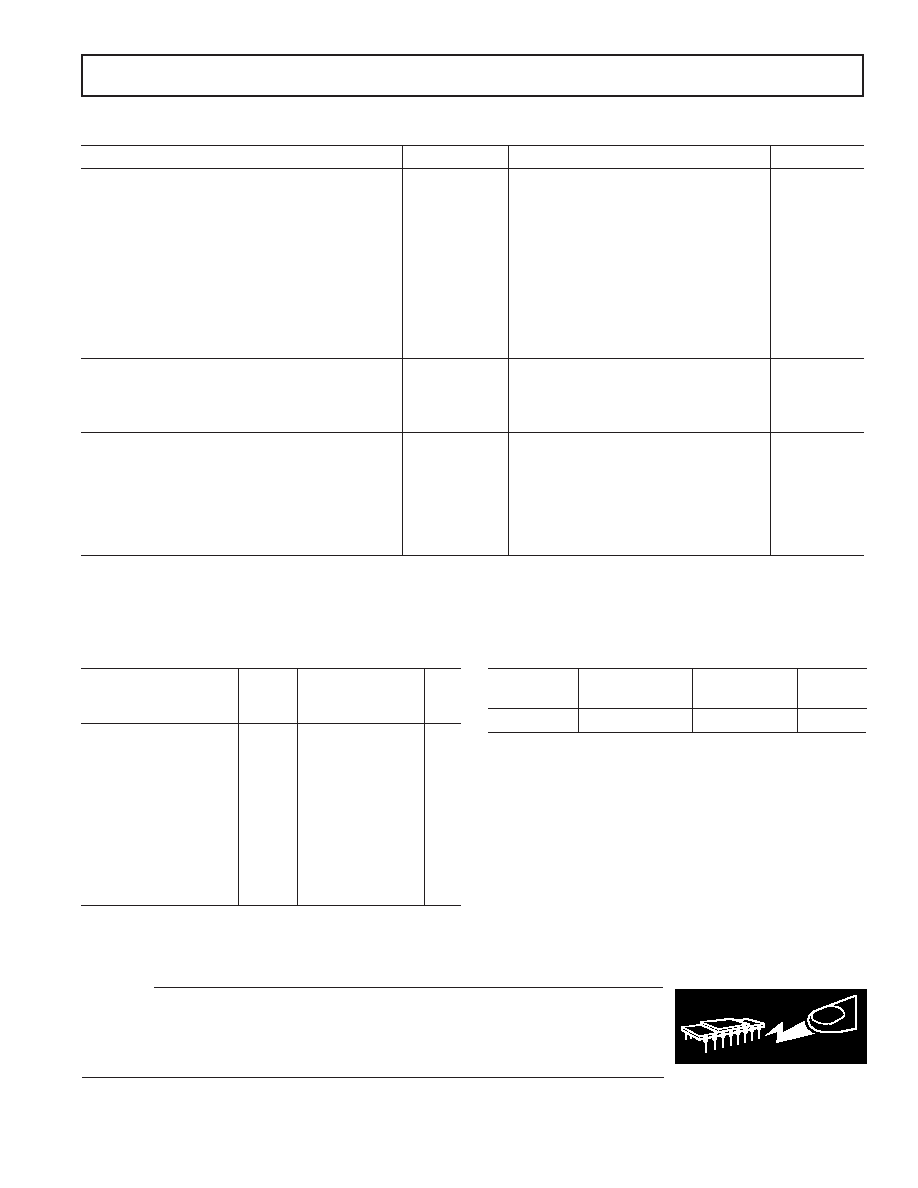

ABSOLUTE MAXIMUM RATINGS

With

Respect

Parameter

To

Min Max

Unit

AVDD1, AVDD2

AVSS

–0.3 +3.9

V

DVDD1, DVDD2

DVSS

–0.3 +3.9

V

DRVDD

DRVSS

–0.3 +3.9

V

Digital Outputs

DRVSS

–0.3 DRVDD + 0.3 V

SHP, SHD, DATACLK

DVSS

–0.3 DVDD + 0.3

V

CLPOB, CLPDM, PBLK

DVSS

–0.3 DVDD + 0.3

V

SCK, SL, SDATA

DVSS

–0.3 DVDD + 0.3

V

VRT, VRB, CMLEVEL

AVSS

–0.3 AVDD + 0.3

V

BYP1-3, CCDIN

AVSS

–0.3 AVDD + 0.3

V

Junction Temperature

150

°C

Lead Temperature (10 sec)

300

°C

TIMING SPECIFICATIONS

Parameter

Symbol

Min

Typ

Max

Unit

SAMPLE CLOCKS

DATACLK, SHP, SHD Clock Period

tCP

33

ns

DATACLK High/Low Pulsewidth

tADC

13

16.7

ns

SHP Pulsewidth

tSHP

5

8.3

ns

SHD Pulsewidth

tSHD

5

8.3

ns

CLPDM Pulsewidth

tCDM

410

Pixels

CLPOB Pulsewidth*

tCOB

220

Pixels

SHP Rising Edge to SHD Falling Edge

tS1

0

8.3

ns

SHP Rising Edge to SHD Rising Edge

tS2

15

16.7

ns

Internal Clock Delay

tID

3.0

ns

Inhibited Clock Period

tINH

10

ns

DATA OUTPUTS

Output Delay

tOD

13

16

ns

Output Hold Time

tH

7.0

7.6

ns

Pipeline Delay

9

Cycles

SERIAL INTERFACE

Maximum SCK Frequency

fSCLK

10

MHz

SL to SCK Setup Time

tLS

10

ns

SCK to SL Hold Time

tLH

10

ns

SDATA Valid to SCK Rising Edge Setup

tDS

10

ns

SCK Falling Edge to SDATA Valid Hold

tDH

10

ns

SCK Falling Edge to SDATA Valid Read

tDV

10

ns

*Minimum CLPOB pulsewidth is for functional operation only. Wider typical pulses are recommended to achieve low noise clamp performance.

Specications subject to change without notice.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD9824 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

(CL = 20 pF, fSAMP = 30 MHz, CCD-Mode Timing in Figures 5 and 6, AUX-Mode Timing in Figure 7,

Serial Timing in Figures 21–24.)

ORDERING GUIDE

Temperature

Package

Model

Range

Description

Option

AD9824KCP

–20

°C to +85°C LFCSP

CP-48

THERMAL CHARACTERISTICS

Thermal Resistance

48-Lead LFCSP Package

θ

JA = 26

°C/W*

*

θ

JA is measured using a 4-layer PCB with the exposed paddle

soldered to the board.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9826KRSZRL | IC IMAGE SGNL PROC 16BIT 28-SSOP |

| AD9830ASTZ-REEL | IC DDS 10BIT 50MHZ CMOS 48TQFP |

| AD9832BRU-REEL | IC DDS 10BIT 25MHZ CMOS 16-TSSOP |

| AD9833BRM | IC WAVEFORM GEN PROG 10-MSOP |

| AD9834BRU | IC DDS W/COMP 2.3V 50MHZ 20TSSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9826 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Complete 16-Bit Imaging Signal Processor |

| AD9826_12 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Complete 16-Bit Imaging Signal Processor |

| AD9826-EB | 制造商:Analog Devices 功能描述:- Bulk |

| AD9826KRS | 制造商:Analog Devices 功能描述:AFE Video 1ADC 16-Bit 5V 28-Pin SSOP Tube 制造商:Analog Devices 功能描述:IC 16-BIT SIGNAL PROCESSOR |

| AD9826KRSRL | 制造商:Analog Devices 功能描述:AFE Video 1ADC 16-Bit 5V 28-Pin SSOP T/R |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。