- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4297 > XC2S30-6VQ100C (Xilinx Inc)IC FPGA 2.5V C-TEMP 100-PQFP PDF資料下載

參數(shù)資料

| 型號: | XC2S30-6VQ100C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 59/99頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 2.5V C-TEMP 100-PQFP |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Spartan®-II |

| LAB/CLB數(shù): | 216 |

| 邏輯元件/單元數(shù): | 972 |

| RAM 位總計: | 24576 |

| 輸入/輸出數(shù): | 60 |

| 門數(shù): | 30000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 100-TQFP |

| 供應(yīng)商設(shè)備封裝: | 100-VQFP(14x14) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁當(dāng)前第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁

Spartan-II FPGA Family: DC and Switching Characteristics

DS001-3 (v2.8) June 13, 2008

Module 3 of 4

Product Specification

62

R

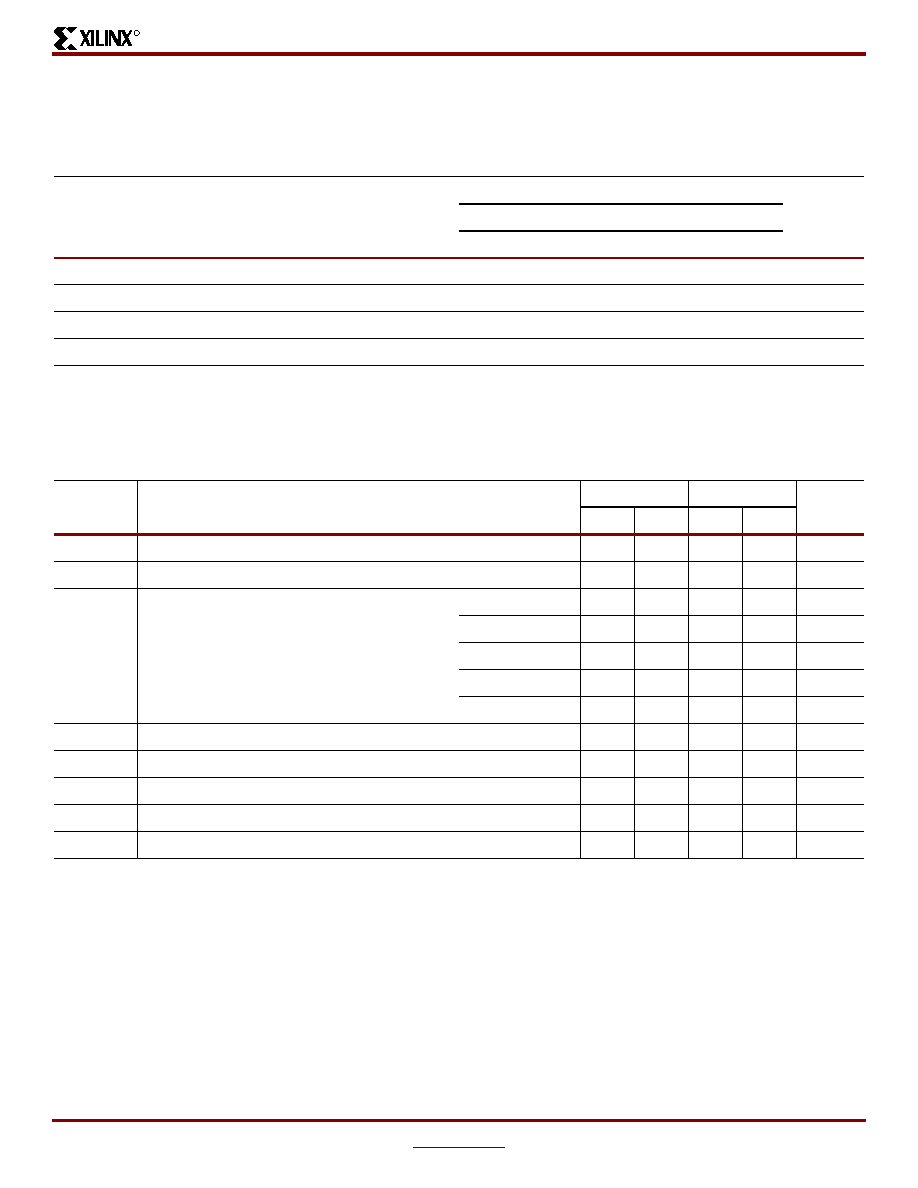

DLL Timing Parameters

All devices are 100 percent functionally tested. Because of

the difficulty in directly measuring many internal timing

parameters, those parameters are derived from benchmark

timing patterns. The following guidelines reflect worst-case

values across the recommended operating conditions.

DLL Clock Tolerance, Jitter, and Phase Information

All DLL output jitter and phase specifications were

determined through statistical measurement at the package

pins using a clock mirror configuration and matched drivers.

Figure 52, page 63, provides definitions for various

parameters in the table below.

Symbol

Description

Speed Grade

Units

-6

-5

Min

Max

Min

Max

FCLKINHF

Input clock frequency (CLKDLLHF)

60

200

60

180

MHz

FCLKINLF

Input clock frequency (CLKDLL)

25

100

25

90

MHz

TDLLPWHF

Input clock pulse width (CLKDLLHF)

2.0

-

2.4

-

ns

TDLLPWLF

Input clock pulse width (CLKDLL)

2.5

-

3.0

-

ns

Symbol

Description

F

CLKIN

CLKDLLHF

CLKDLL

Units

Min

Max

Min

Max

TIPTOL

Input clock period tolerance

-

1.0

-

1.0

ns

TIJITCC

Input clock jitter tolerance (cycle-to-cycle)

-

±150

-

±300

ps

TLOCK

Time required for DLL to acquire lock

> 60 MHz

-

20

-

20

μs

50-60 MHz

-

25

μs

40-50 MHz

-

50

μs

30-40 MHz

-

90

μs

25-30 MHz

-

120

μs

TOJITCC

Output jitter (cycle-to-cycle) for any DLL clock output(1)

-

±60

-

±60

ps

TPHIO

Phase offset between CLKIN and CLKO(2)

-

±100

-

±100

ps

TPHOO

Phase offset between clock outputs on the DLL(3)

-

±140

-

±140

ps

TPHIOM

Maximum phase difference between CLKIN and CLKO(4)

-

±160

-

±160

ps

TPHOOM

Maximum phase difference between clock outputs on the DLL(5)

-

±200

-

±200

ps

Notes:

1.

Output Jitter is cycle-to-cycle jitter measured on the DLL output clock, excluding input clock jitter.

2.

Phase Offset between CLKIN and CLKO is the worst-case fixed time difference between rising edges of CLKIN and CLKO,

excluding output jitter and input clock jitter.

3.

Phase Offset between Clock Outputs on the DLL is the worst-case fixed time difference between rising edges of any two DLL

outputs, excluding Output Jitter and input clock jitter.

4.

Maximum Phase Difference between CLKIN an CLKO is the sum of Output Jitter and Phase Offset between CLKIN and CLKO,

or the greatest difference between CLKIN and CLKO rising edges due to DLL alone (excluding input clock jitter).

5.

Maximum Phase Difference between Clock Outputs on the DLL is the sum of Output JItter and Phase Offset between any DLL

clock outputs, or the greatest difference between any two DLL output rising edges due to DLL alone (excluding input clock jitter).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP4S100G5F45I3N | IC STRATIX IV FPGA 530K 1932FBGA |

| 24LCS52-I/MS | IC EEPROM 2KBIT 400KHZ 8MSOP |

| ABC60DREH-S13 | CONN EDGECARD 120PS .100 EYELET |

| ACC60DREH-S13 | CONN EDGECARD 120POS .100 EYELET |

| XC2S30-5VQ100I | IC FPGA 2.5V I-TEMP 100-VQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S30-6VQ100I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II 2.5V FPGA Family:Introduction and Ordering Information |

| XC2S30-6VQG100C | 制造商:Xilinx 功能描述:FPGA SPARTAN-II 30K GATES 972 CELLS 263MHZ 2.5V 100VTQFP - Trays |

| XC2S30-6VQG100I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II FPGA Family |

| XC2S400E | 制造商:XILINX 制造商全稱:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMS |

| XC2S400E-6FG456C | 制造商:Xilinx 功能描述:FPGA SPARTAN-IIE 400K GATES 10800 CELLS 357MHZ 1.8V 456FBGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。