- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1973 > XA3SD3400A-4FGG676I (Xilinx Inc)SPARTAN-3ADSP FPGA 3400K 676FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XA3SD3400A-4FGG676I |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 34/58頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | SPARTAN-3ADSP FPGA 3400K 676FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Extended Spartan 3A FPGA Family |

| 標(biāo)準(zhǔn)包裝: | 40 |

| 系列: | Spartan®-3A DSP XA |

| LAB/CLB數(shù): | 5968 |

| 邏輯元件/單元數(shù): | 53712 |

| RAM 位總計(jì): | 2322432 |

| 輸入/輸出數(shù): | 469 |

| 門數(shù): | 3400000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 676-BGA |

| 供應(yīng)商設(shè)備封裝: | 676-FBGA(27x27) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)當(dāng)前第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)

XA Spartan-3A DSP Automotive FPGA Family Data Sheet

DS705 (v2.0) April 18, 2011

Product Specification

4

I/O Capabilities

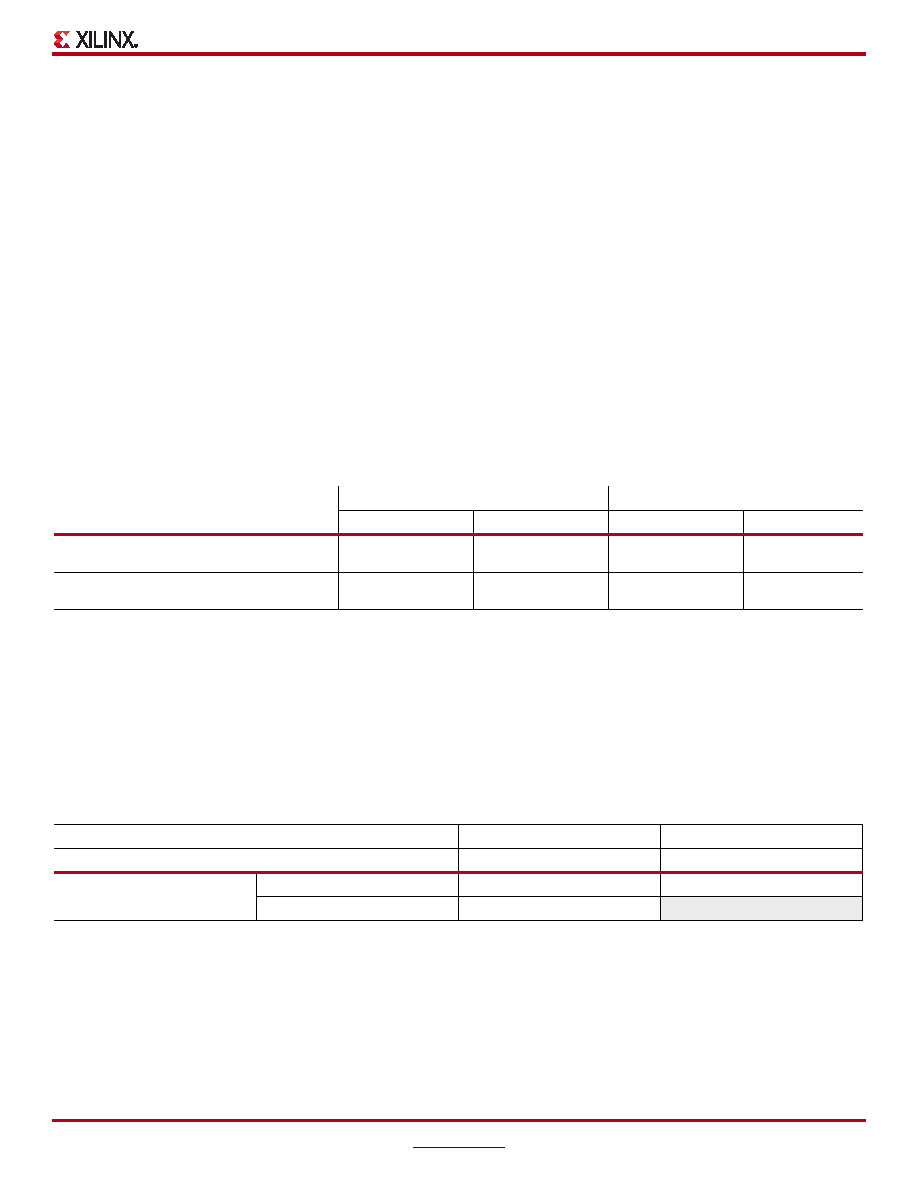

The XA Spartan-3A DSP FPGA SelectIO interface supports many popular single-ended and differential standards. Table 2

shows the number of user I/Os as well as the number of differential I/O pairs available for each device/package combination.

Some of the user I/Os are unidirectional input-only pins as indicated in Table 2.

XA Spartan-3A DSP FPGAs support the following single-ended standards:

3.3V low-voltage TTL (LVTTL)

Low-voltage CMOS (LVCMOS) at 3.3V, 2.5V, 1.8V, 1.5V, or 1.2V

3.3V PCI at 33 MHz

HSTL I, II, and III at 1.5V and 1.8V, commonly used in memory applications

SSTL I and II at 1.8V, 2.5V, and 3.3V, commonly used for memory applications

XA Spartan-3A DSP FPGAs support the following differential standards:

LVDS, mini-LVDS, RSDS, and PPDS I/O at 2.5V or 3.3V

Bus LVDS I/O at 2.5V

TMDS I/O at 3.3V

Differential HSTL and SSTL I/O

LVPECL inputs at 2.5V or 3.3V

Production Status

Table 3 indicates the production status of each XA Spartan-3A DSP FPGA by temperature range and speed grade. The

table also lists the earliest speed file version required for creating a production configuration bitstream. Later versions are

also supported.

Table 2: Available User I/Os and Differential I/O Pairs

Device

CSG484

FGG676

User

Differential

User

Differential

XA3SD1800A

309

(60)

140

(78)

519

(110)

227

(131)

XA3SD3400A

309

(60)

140

(78)

469

(60)

213

(117)

Notes:

1.

The number shown in bold indicates the maximum number of I/O and input-only pins. The number shown in (italics) indicates the number

of input-only pins. The differential input-only pin count includes both differential pairs on input-only pins and differential pairs on I/O pins

within I/O banks that are restricted to differential inputs.

Table 3: XA Spartan-3A DSP FPGA Family Production Status (Production Speed File)

Temperature Range

I-Grade

Q-Grade

Speed Grade

Standard (-4)

Part Number

XA3SD1800A

Production (v1.32)

XA3SD3400A

Production (v1.32)

–

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XA6SLX75T-3FGG484Q | IC FPGA SPARTAN 6 484FGGBGA |

| XA95144XL-15CSG144I | IC CPLD 144MC 117 I/O 144CSBGA |

| XAM1808AZCE4 | IC ARM PROCESSOR 361NFBGA |

| XC1765ESOG8C | IC PROM SERIAL 65K 8-SOIC |

| XC17S200AVQ44I | IC PROM SER 200000 I-TEMP 44VQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X-A4A-300L | 制造商:Leach International Corporation 功能描述:MID RANGE - Bulk |

| X-A4C-300M | 制造商:Leach International Corporation 功能描述:MID RANGE - Bulk |

| X-A4M-300L | 制造商:Leach International Corporation 功能描述:MID RANGE - Bulk |

| X-A4M-300M | 制造商:Leach International Corporation 功能描述:MID RANGE - Bulk |

| X-A4N | 制造商:Leach International Corporation 功能描述:MID RANGE - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。