- 您現(xiàn)在的位置:買賣IC網 > PDF目錄199412 > TMP86CH09NG 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PDIP32 PDF資料下載

參數資料

| 型號: | TMP86CH09NG |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PDIP32 |

| 封裝: | 0.400 INCH, 1.78 MM PITCH, LEAD FREE, PLASTIC, SDIP-32 |

| 文件頁數: | 7/120頁 |

| 文件大小: | 1743K |

| 代理商: | TMP86CH09NG |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁

Page 93

TMP86FH09ANG

9.3.4 8-Bit Pulse Width Modulation (PWM) Output Mode (TC3, 4)

This mode is used to generate a pulse-width modulated (PWM) signals with up to 8 bits of resolution. The

up-counter counts up using the internal clock.

When a match between the up-counter and the PWREGj value is detected, the logic level output from the

timer F/Fj is switched to the opposite state. The counter continues counting. The logic level output from the

timer F/Fj is switched to the opposite state again by the up-counter overflow, and the counter is cleared. The

INTTCj interrupt request is generated at this time.

Since the initial value can be set to the timer F/Fj by TCjCR<TFFj>, positive and negative pulses can be gen-

erated. Upon reset, the timer F/Fj is cleared to 0.

(The logic level output from the PWMj pin is the opposite to the timer F/Fj logic level.)

Since PWREGj in the PWM mode is serially connected to the shift register, the value set to PWREGj can be

changed while the timer is running. The value set to PWREGj during a run of the timer is shifted by the

INTTCj interrupt request and loaded into PWREGj. While the timer is stopped, the value is shifted immedi-

ately after the programming of PWREGj. If executing the read instruction to PWREGj during PWM output,

the value in the shift register is read, but not the value set in PWREGj. Therefore, after writing to PWREGj, the

reading data of PWREGj is previous value until INTTCj is generated.

For the pin used for PWM output, the output latch of the I/O port must be set to 1.

Note 1: In the PWM mode, program the timer register PWREGj immediately after the INTTCj interrupt request is

generated (normally in the INTTCj interrupt service routine.) If the programming of PWREGj and the inter-

rupt request occur at the same time, an unstable value is shifted, that may result in generation of the pulse

different from the programmed value until the next INTTCj interrupt request is generated.

Note 2: When the timer is stopped during PWM output, the PWMj pin holds the output status when the timer is

stopped. To change the output status, program TCjCR<TFFj> after the timer is stopped. Do not change the

TCjCR<TFFj> upon stopping of the timer.

Example: Fixing the PWMj pin to the high level when the TimerCounter is stopped

CLR (TCjCR).3: Stops the timer.

CLR (TCjCR).7: Sets the PWMj pin to the high level.

Note 3: To enter the STOP mode during PWM output, stop the timer and then enter the STOP mode. If the STOP

mode is entered without stopping the timer when fc, fc/2 or fs is selected as the source clock, a pulse is out-

put from the PWMj pin during the warm-up period time after exiting the STOP mode.

Note 4: j = 3, 4

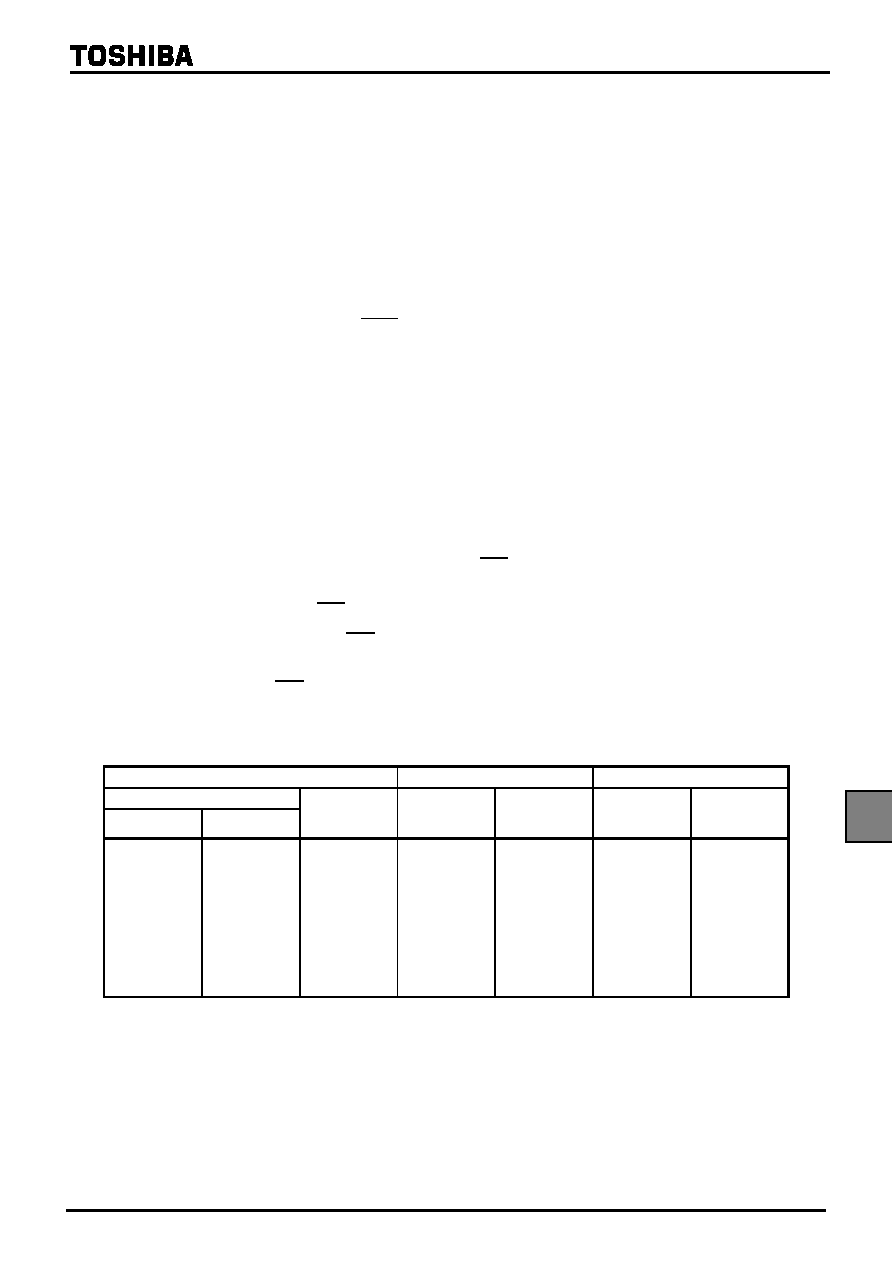

Table 9-5 PWM Output Mode

Source Clock

Resolution

Repeated Cycle

NORMAL1/2, IDLE1/2 mode

SLOW1/2,

SLEEP1/2

mode

fc = 16 MHz

fs = 32.768 kHz

fc = 16 MHz

fs = 32.768 kHz

DV7CK = 0

DV7CK = 1

fc/211 [Hz]

fs/23 [Hz]

128

s244.14 s

32.8 ms

62.5 ms

fc/27

–8

s–

2.05 ms

–

fc/25

–2

s

–

512

s–

fc/23

–

500 ns

–

128

s–

fs

30.5

s30.5 s

7.81 ms

fc/2

–

125 ns

–

32

s–

fc

–

62.5 ns

–

16

s–

相關PDF資料 |

PDF描述 |

|---|---|

| TMP86CM29BU | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP64 |

| TMP86FH09NG | 8-BIT, FLASH, 16 MHz, MICROCONTROLLER, PDIP32 |

| TMP86FS49BUG | 8-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQFP64 |

| TMP86PS25F | 8-BIT, OTPROM, 16 MHz, MICROCONTROLLER, PQFP100 |

| TMP87C800N | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP64 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TMP86CH12MG | 制造商:TOSHIBA 制造商全稱:Toshiba Semiconductor 功能描述:8 Bit Microcontroller |

| TMP86CH21AUG | 制造商:TOSHIBA 制造商全稱:Toshiba Semiconductor 功能描述:8 Bit Microcontroller |

| TMP86CH21F | 制造商:TOSHIBA 制造商全稱:Toshiba Semiconductor 功能描述:CMOS 8-Bit Microcontroller |

| TMP86CH21U | 制造商:TOSHIBA 制造商全稱:Toshiba Semiconductor 功能描述:CMOS 8-Bit Microcontroller |

| TMP86CH22UG | 制造商:TOSHIBA 制造商全稱:Toshiba Semiconductor 功能描述:8 Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。