- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄297500 > TL16PNP100APT (TEXAS INSTRUMENTS INC) SPECIALTY MICROPROCESSOR CIRCUIT, PQFP48 PDF資料下載

參數(shù)資料

| 型號: | TL16PNP100APT |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PQFP48 |

| 封裝: | PLASTIC, QFP-48 |

| 文件頁數(shù): | 15/21頁 |

| 文件大小: | 304K |

| 代理商: | TL16PNP100APT |

TL16PNP100A

STANDALONE PLUG-AND-PLAY (PnP) CONTROLLER

SLLS200C – MARCH 1995 – REVISED SEPTEMBER 1997

3

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

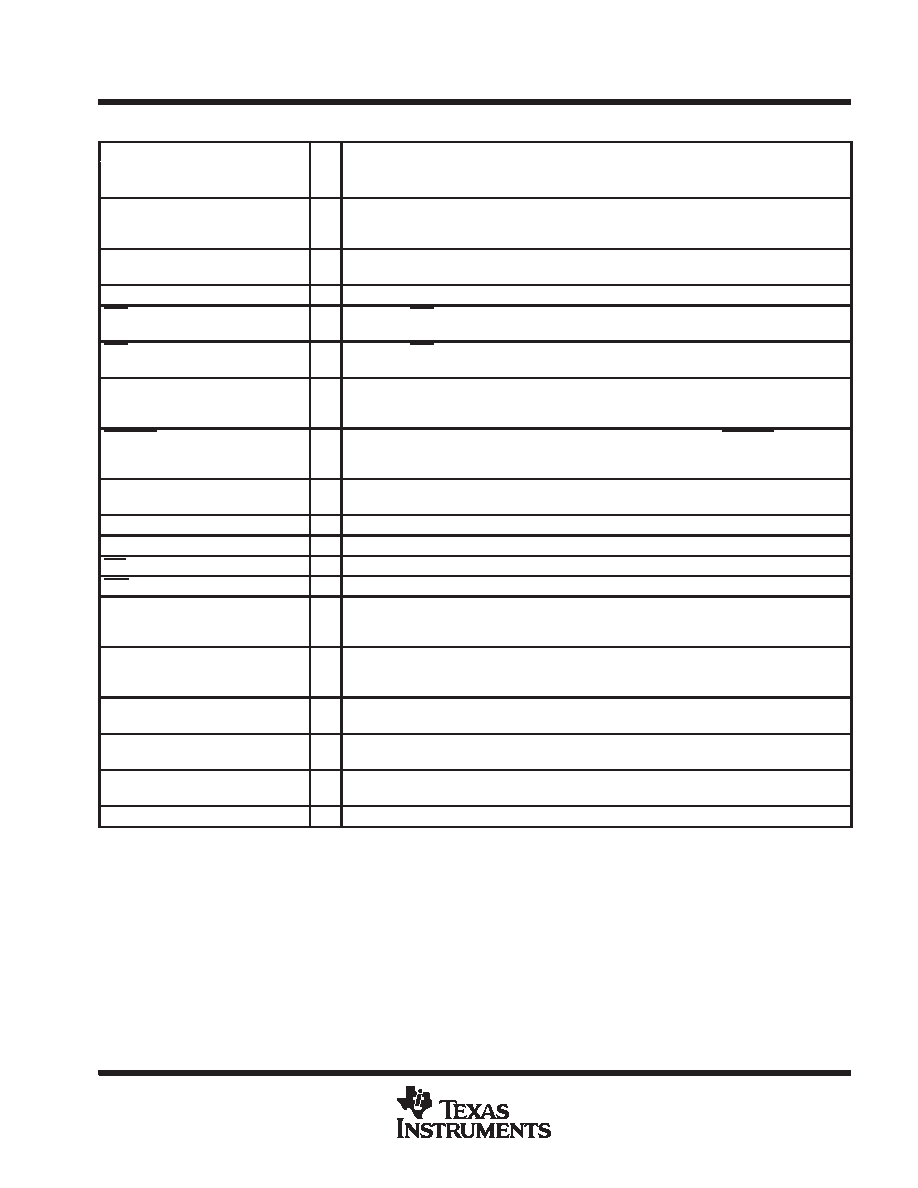

Terminal Functions

TERMINAL

NAME

FN

NO.

PT

NO.

I/O

DESCRIPTION

A0

A11–A1

1

44 – 34

42

41 – 33,

31, 30

I

12-bit ISA address terminals. A0 and A1 – A11 are used during the PnP autoconfiguration

sequence.

AEN

6

48

I

ISA address enable. AEN is active during DMA operation and causes the controller to ignore the

ISA transaction.

CLK

32

28

I

22-MHz external clock input. CLK synchronizes PnP logic and generates a 0.68-MHz SCLK.

CS0

30

26

O

Chip select. CS0 is used for logical device number 0. The address decoder only decodes a 10-bit

address for one I/O location with programmable block size.

CS1

23

18

O

Chip select. CS1 is used for logical device number 1 . The address decoder only decodes a 10-bit

address for one I/O location with programmable block size.

D0 – D3

D4 – D7

7–10

12 – 15

1–4

6,8 – 10

I/O

Data bus. D0–D3 and D4–D7 with 3-state outputs provide a bidirectional path for data, control,

and status information between the TL16PNP100A and the CPU. Output drive sinks 24 mA at

0.4 V and sources 12 mA at 2.4 V.

EEPROM

29

25

I/O

EEPROM interface access enable. A 3-state bidirectional signal. When EEPROM is pulled low,

the EEPROM interface is being accessed. A release state indicates the EEPROM interface is

idle. A 100

A pullup transistor is connected internally to this terminal.

GND

11, 16,

33

5, 11,

29

Ground (0 V). All terminals must be tied to GND for proper operation.

INTR0

31

27

I

Interrupt request from logical device number 0. INTR0 is an active-high signal.

INTR1

24

19

I

Interrupt request from logical device number 1. INTR1 is an active-high signal.

IOR

5

47

I

ISA read input

IOW

4

46

I

ISA write input

IRQ3 – IRQ7

IRQ9

17 – 21

22

12 – 16

17

O

Interrupt request. INTRn request is mapped to one of the IRQs based on the value of the content

of the interrupt request level (0

×70) register. Output drive sinks 24 mA at 0.4 V and sources

12 mA at 2.4 V. These terminals are 3-state outputs.

RESET

3

45

I

Reset. When active (high), RESET clears most logical device registers and puts the

TL16PNP100A in the wait-for-key state. The CSN is reset to 0

×0. All configuration registers are

set to their power-up values.

SCLK

26

22

I/O

Serial clock (3-state output path). SCLK controls the serial bus timing for address data. A 100-

A

pulldown transistor is connected internally to this terminal.

SCS

27

23

I/O

EEPROM chip select (3-state output). SCS controls the activity of the EEPROM. A 100-

A

pulldown transistor is connected internally to this terminal.

SIO

28

24

I/O

Serial input/output. A 3-state bidirectional EEPROM I/O data path. A 100

A pulldown transistor

is connected internally to this terminal.

VCC

2, 25

21, 43

5-V supply voltage

相關PDF資料 |

PDF描述 |

|---|---|

| TL431BU | 1-OUTPUT THREE TERM VOLTAGE REFERENCE, PDSO3 |

| TLE4252D | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PSSO4 |

| TLK4201EARGTRG4 | 4.25-GBPS CABLE AND PC BOARD EQUALIZER |

| TLK4201EARGTR | 4.25-GBPS CABLE AND PC BOARD EQUALIZER |

| TLK4201EARGTTG4 | 4.25-GBPS CABLE AND PC BOARD EQUALIZER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TL16PNP200 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:STANDALONE PLUG-AND-PLAY (PnP) CONTROLLER |

| TL16PNP200A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:STANDALONE PLUG-AND-PLAY (PnP) CONTROLLER |

| TL16PNP550A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ASYNCHRONOUS COMMUNICATIONS ELEMENT WITH PLUG-AND-PLAY (PnP) AND AUTOFLOW CONTROL |

| TL16PNP550AFN | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TL-17 | 功能描述:手工工具 TOOL RoHS:否 制造商:Molex 產(chǎn)品:Extraction Tools 類型: 描述/功能:Extraction tool |

發(fā)布緊急采購,3分鐘左右您將得到回復。