- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372115 > SAA7390GP (NXP Semiconductors N.V.) High performance Compact Disc-Recordable CD-R controller PDF資料下載

參數(shù)資料

| 型號(hào): | SAA7390GP |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | High performance Compact Disc-Recordable CD-R controller |

| 中文描述: | 高性能式光盤CD - R光盤控制器 |

| 文件頁(yè)數(shù): | 30/76頁(yè) |

| 文件大?。?/td> | 366K |

| 代理商: | SAA7390GP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)

1996 Jul 02

30

Philips Semiconductors

Preliminary specification

High performance Compact

Disc-Recordable (CD-R) controller

SAA7390

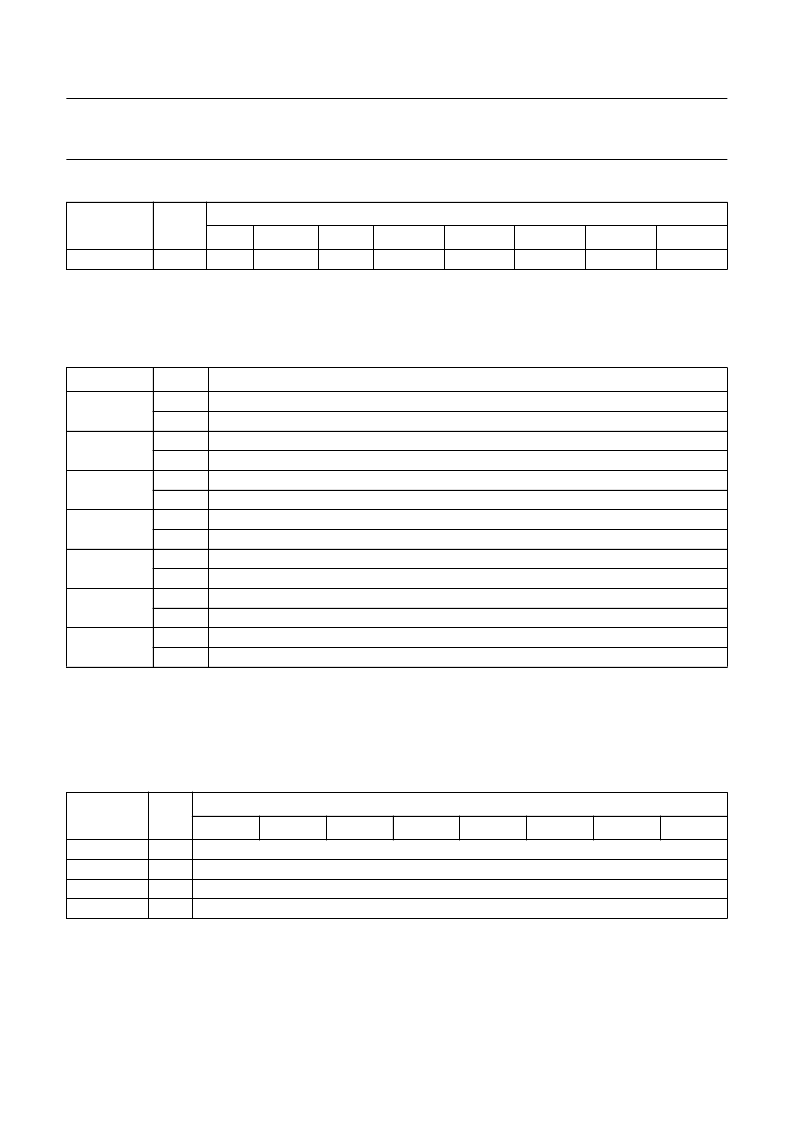

Table 34

SCSI mode control register: 0xF0FD; note 1

Note

1.

Register 0xF0FD controls the operation of the interface to the host interface controller. The outputs of these registers

are used to directly control DRAM access cycles, and will affect any current DRAM cycle in progress.

Table 35

HOSTMOD field descriptions

10 FRONT-END

This chapter explains the information of the front-end circuitry.

10.1

Minute-second frame addressing and header information

Table 36

Header mode and MSF from block decoder: 0xF092, F093, F09A and F09B; note 1

Note

1.

These registers contain the mode, minute, second and frame information from the header when in data mode. This

data is valid whenever the HDDRDY bit in the RDDSTAT register is set. In audio mode, the MSF address is taken

from the Q-channel information.

MNEMONIC

R/W

DATA BYTE

7

6

5

4

3

2

1

0

HOSTMOD

R/W

SELCF92

FAST

OFF_ADR

OFF_END

OFF_STR

RD_BUF

BYT/PAG

FIELD

LOGIC

DESCRIPTION

BYT/PAG

0

1

0

1

0

1

0

1

0

1

0

1

0

1

host interface DRAM byte mode access

host interface DRAM page mode access

host interface read/write control; read from buffer memory

host interface read/write control; write to buffer memory

host interface offset start A/B control; select A registers

host interface offset start A/B control; select B registers

host interface offset end A/B control; select A registers

host interface offset end A/B control; select B registers

host interface transfers use only A registers

host interface transfers use A and B registers

3 cycles host interface burst accesses from buffer

2 cycles host interface burst accesses from buffer

DRAM timing optimized for 53CF90

DRAM timing optimized for 53CF92

RD_BUF

OFF_STR

OFF_END

OFF_ADR

FAST

SELCF92

MNEMONIC

R/W

DATA BYTE

7

6

5

4

3

2

1

0

HDRMODE

HDRMINS

HDRSEC

HDRFRM

R

R

R

R

MODE7 to MODE0

MINUTES7 to MINUTES0

SECONDS7 to SECONDS0

FRAME7 to FRAME0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7501WP | ARD/ZDF NR.3R1 DIGITAL DECODER|LDCC|68PIN|PLASTIC |

| SAA7707H | Shaft; Style: 1 - light; Applicable Model: LE-P / LEL-W |

| SAA7710T | High Quality Audio-Performance Digital Add-On Processor For Digital Sound Systems.(應(yīng)用在數(shù)字聲音系統(tǒng)的高品質(zhì)音頻性能數(shù)字附加處理器) |

| SAA7715AH | Digital Signal Processor |

| SAA7715 | Digital Signal Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7391 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ATAPI CD-R block encoder/decoder |

| SAA7391H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ATAPI CD-R block encoder/decoder |

| SAA7392 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Channel encoder/decoder CDR60 |

| SAA7392HL | 制造商:NXP Semiconductors 功能描述:CD-ROM INTERFACE, 80 Pin, Plastic, QFP |

| SAA7500 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital satellite radio broadcasting tuner decoder SAT-2 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。