- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382380 > PCD5013H (NXP SEMICONDUCTORS) FLEX roaming decoder II PDF資料下載

參數(shù)資料

| 型號(hào): | PCD5013H |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 尋呼電路 |

| 英文描述: | FLEX roaming decoder II |

| 中文描述: | TELECOM, PAGING DECODER, PQFP32 |

| 封裝: | 7 X 7 MM, 1.40 MM HEIGHT, PLASTIC, SOT-358-1, LQFP-32 |

| 文件頁(yè)數(shù): | 32/76頁(yè) |

| 文件大小: | 270K |

| 代理商: | PCD5013H |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)當(dāng)前第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)

1999 Apr 12

32

Philips Semiconductors

Product specification

FLEX

roaming decoder II

PCD5013

8.5.6.2

Receiver on setting packets (ID = 16H to 19H)

LBC:

low battery check (Tables 24 and 25). If this bit is

set, the PCD5013 checks the status of the LOBAT port just

before leaving this receiver sync setting state. Value after

reset = 0.

CLS:

control line setting (Tables 24 and 25). This is the

value to be output on the receiver control lines for this

receiver sync setting state. Value after reset = 0.

ST:

step time (Table 24). This sets the waiting time, before

expecting good signals at EXTS1 and EXTS0 at the end of

the warm-up sequence, after turning decoding on.

The setting is in steps of 625

μ

s. Valid values are:

625

μ

s (ST = 01H) to 79.375 ms (ST = 7FH). Value after

reset = 01H.

s:

setting number, see Tables 23 and 25 for the s names

and values and location in the receiver on setting packet.

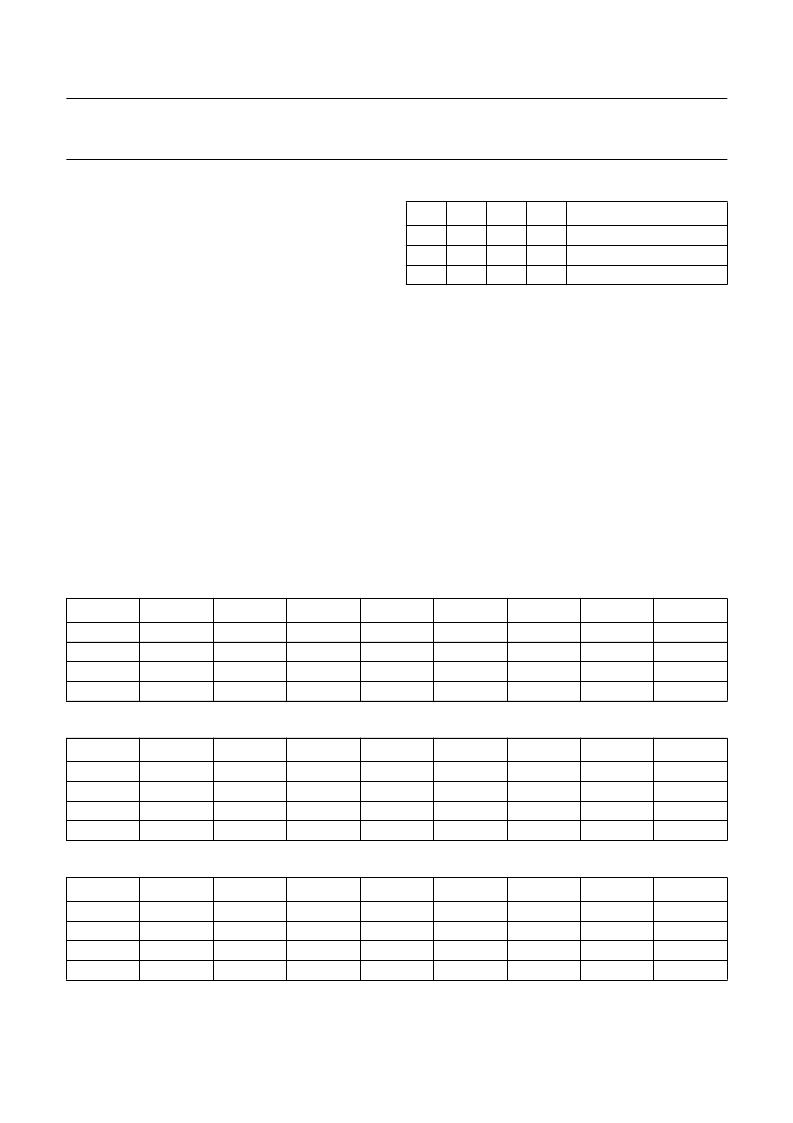

Table 23

s names and values

8.5.7

F

ORCING RECEIVER LINES

(ID = 0FH)

This packet (Table 26) enables host control over the

receiver control line (S0 to S7) settings in all modes except

reset. In reset, the receiver control lines are high

impedance.

FRS:

force receiver setting (Table 26). Setting a bit causes

the associated CLS bit in this packet to override the

internal receiver control settings on the corresponding

receiver control line. Clearing a bit returns control of the

corresponding receiver control line to the PCD5013. Value

after reset = 0.

CLS:

control line setting (Table 26). This bit setting is

applied to the corresponding receiver control line if the

associated FRS bit is set in this packet. Value after

reset = 0.

s

3

0

1

1

s

2

1

0

0

s

1

1

0

0

s

0

1

0

1

SETTING NAME

1600 sps sync

3200 sps data

1600 sps data

Table 24

3200 sps sync setting packet bit assignments

Table 25

Receiver on setting packet bit assignments

Table 26

Receiver line control packet bit assignments

BYTE

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

3

2

1

0

0

0

0

0

0

0

1

0

0

1

0

1

0

0

0

LBC

CLS

3

ST

3

CLS

7

0

CLS

6

ST

6

CLS

5

ST

5

CLS

4

ST

4

CLS

2

ST

2

CLS

1

ST

1

CLS

0

ST

0

BYTE

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

3

2

1

0

0

0

0

0

0

0

1

0

s

3

s

2

0

s

1

0

s

0

0

LBC

CLS

3

0

CLS

7

0

CLS

6

0

CLS

5

0

CLS

4

0

CLS

2

0

CLS

1

0

CLS

0

0

BYTE

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

3

2

1

0

0

0

0

0

0

0

0

0

1

0

1

0

1

0

1

0

FRS

7

CLS

7

FRS

6

CLS

6

FRS

5

CLS

5

FRS

4

CLS

4

FRS

3

CLS

3

FRS

2

CLS

2

FRS

1

CLS

1

FRS

0

CLS

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCD5032 | ADPCM CODEC for digital cordless telephones |

| PCD5032H | ADPCM CODEC for digital cordless telephones |

| PCD5032T | ADPCM CODEC for digital cordless telephones |

| PCD5041 | DECT burst mode controller |

| PCD5041H | DECT burst mode controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCD5032 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ADPCM CODEC for digital cordless telephones |

| PCD5032B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Linear CODEC |

| PCD5032D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Linear CODEC |

| PCD5032H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ADPCM CODEC for digital cordless telephones |

| PCD5032T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ADPCM CODEC for digital cordless telephones |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。