- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359265 > MX98727 SINGLE CHIP PCI/CARDBUS FAST ETHERNET CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | MX98727 |

| 英文描述: | SINGLE CHIP PCI/CARDBUS FAST ETHERNET CONTROLLER |

| 中文描述: | 單芯片的PCI / CARDBUS快速以太網(wǎng)控制器 |

| 文件頁數(shù): | 31/71頁 |

| 文件大?。?/td> | 389K |

| 代理商: | MX98727 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁

31

P/N:PM0723

REV. 1.0, JUL. 13, 2000

MX98728EC

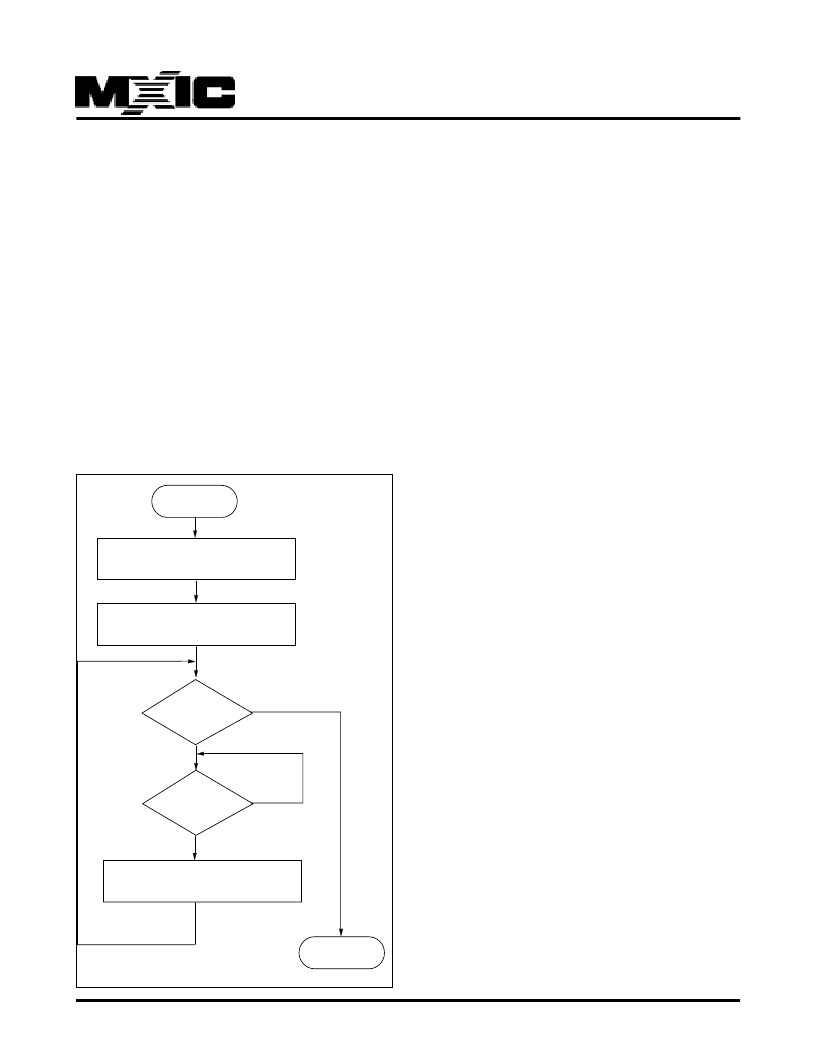

During the process of filling up packet(s) in the transmit

buffer ring, the current write address to the TX buffer

ring is controlled by GMAC using TWP and TWPBC to

form packet memory's address lines. TWP is updated

by the driver only and TWP checked against

TRP,BP,TLBP by both GMAC and the driver to maintain

TX buffer ring's integrity. TWP serves as the start page

of non-ready packet(s) which is still being prepared by

the driver. The following flow chart shows the typical way

of preparing a packet in the packet buffer. (for systems

without the SRDY pin support).

Conditions required to begin transmission

1. Register 00h.ST1=0 and Reg00h.ST0=1 in the TX lo-

cal DMA mode or register 00h.ST1=1 and ST0=0 in

the direct FIFO mode

2. The interframe gap timer has timed out.

3. The TX FIFO is filled with a complete packet or is full.

4. If a collision has been detected and the backoff timer

has expired.

After the packet starts to go out to the network, TTHD[1:0]

will begin to affect the packet memory's arbitration if the

FIFO needs more data from the packet memory( TTHD

is not used in the direct FIFO mode ). In the TX local

DMA mode, the advantage of the smaller threshold is to

reduce the risk of a potential transmit FIFO underrun

error for large packets beyond 1518 bytes. Such underrun

error occurs when all the data in the FIFO is transmitted

while the local DMA still has not filled in more data to be

transmitted. Since the TX FIFO is large enough for the

largest normal packet ( 1518 bytes ), the TTHD and FIFO

underrun applies to packets larger than 1518 bytes in

the TX local DMA mode. The larger the TTHD, the less

aggressive the TX DMA is in the packet memory arbitra-

tion. Therefore the host and the RX DMA may have

more bandwidth in the packet memory.

When this underrun occurs, the packet will be aborted

and an interrupt will be asserted to get the host's atten-

tion. The FIFOEI ( register 09h bit 5 ) interrupt bit will be

set when the underrun occurs and an interrupt to the

host is asserted if the FIFOEIM bit (register 08h bit 5 )

is also set.

bit ) of the descriptor needs to be set to 1 to indicate that

the device driver has finished preparing the current

packet. Then the packet can be transferred to GMAC for

transmission. At this point, the TX DMA poll command

can be issued by setting Reg00h.ST1=0, ST0=1 to ac-

tivate the transmit operation. ST1 and ST0 bits will be

cleared to 0 and TXDMA[3:0]=1h when the transmission

is done.

START

Yes

Next data write

Exit Write

Processing

Yes

Write starting page address to TWP

(0E/0F)

Read

WRDYB

(3A.0)==0

First data write to TX Registers

(34-37)

Next data write to TX Register

(34-37)

No

No

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MX98742 | FEBC 100 Base Fast Ethernet Bridge Controller |

| MX98902A(PLCC) | LAN Node Controller |

| MX98902A(PQFP) | LAN Node Controller |

| MX98902A(SQFP) | LAN Node Controller |

| MX99011MC | Interface IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MX98728 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:GMAC SINGLE CHIP 10/100 FAST ETHERNET CONTROLLER FOR GENERIC APPLICATION |

| MX98728AEC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| MX98728EC | 制造商:MCNIX 制造商全稱:Macronix International 功能描述:GMAC SINGLE CHIP 10/100 FAST ETHERNET CONTROLLER FOR GENERIC APPLICATION |

| MX98741 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| MX98742 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FEBC 100 Base Fast Ethernet Bridge Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。