- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45312 > MCF5471ZP200 (MOTOROLA INC) 32-BIT, 200 MHz, RISC PROCESSOR, PBGA388 PDF資料下載

參數(shù)資料

| 型號(hào): | MCF5471ZP200 |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA388 |

| 封裝: | 27 X 27 MM, 1 MM PITCH, PLASTIC, MS-034AAL-1, BGA-388 |

| 文件頁數(shù): | 30/96頁 |

| 文件大?。?/td> | 2003K |

| 代理商: | MCF5471ZP200 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當(dāng)前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

36

MCF547x Integrated Microprocessor Hardware Specifications

MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

Signal Description

1.5.1.6.6

AD[1:0]—Port Size Configuration (PSCONFIG)

The default port size value of the boot FBCS0 is determined by the logic levels driven on AD[1:0] at the

rising edge of RSTI, which are reflected as the reset value of CSCR0[PS]. Table 11 shows how the logic

levels of AD[1:0] correspond to the FBCS0 port size at reset.

1.5.1.7

Ethernet Module Signals

The following signals are used by the Ethernet module for data and clock signals.

1.5.1.7.1

Management Data (E0MDIO, E1MDIO)

The bidirectional EMDIO signals transfer control information between the external PHY and the

media-access controller. Data is synchronous to EMDC and applies to MII mode operation. This signal is

an input after reset. When the FEC operates in 10 Mbps 7-wire interface mode, this signal should be

connected to VSS.

1.5.1.7.2

Management Data Clock (E0MDC, E1MDC)

EMDC is an output clock which provides a timing reference to the PHY for data transfers on the EMDIO

signal and applies to MII mode operation.

1.5.1.7.3

Transmit Clock (E0TXCLK, E1TXCLK)

This is an input clock which provides a timing reference for ETXEN, ETXD[3:0] and ETXER.

1.5.1.7.4

Transmit Enable (E0TXEN, E1TXEN)

The transmit enable (ETXEN) output indicates when valid nibbles are present on the MII. This signal is

asserted with the first nibble of a preamble and is negated before the first ETXCLK following the final

nibble of the frame.

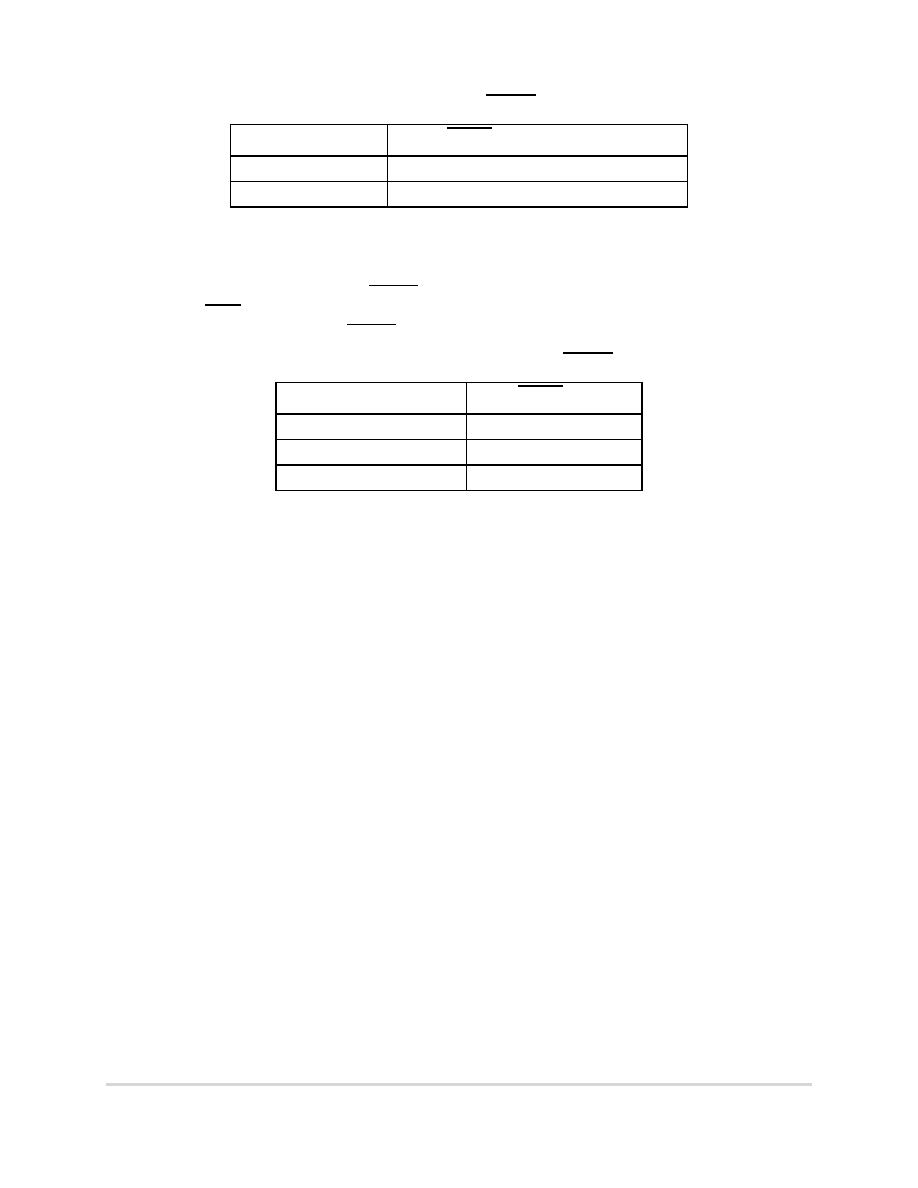

Table 10. AD2/AA_CONFIG Selection of FBCS0 Automatic Acknowledge

AD2

Boot FBCS0 AA Configuration at Reset

0

Disabled

1

Enabled with 63 wait states

Table 11. AD[1:0]/PSCONFIG[1:0] Selection of FBCS0 Port Size

AD[1:0]

Boot FBCS0 Port Size

00

32-bit port

01

8-bit port

1X

16-bit port

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCF5472VR200 | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA388 |

| MCF5475VR266 | 32-BIT, 266.66 MHz, RISC PROCESSOR, PBGA388 |

| MCF5470ZP200 | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA388 |

| MCF5475ZP266 | 32-BIT, 266.66 MHz, RISC PROCESSOR, PBGA388 |

| MCF5471ZP200 | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA388 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCF5472 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MCF547x Integrated Microprocessor Electrical Characteristics |

| MCF5472EC | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MCF547x ColdFire Microprocessor |

| MCF5472VR200 | 功能描述:微處理器 - MPU MCF547X V4ECORE MMU FPU RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MCF5472ZP200 | 功能描述:微處理器 - MPU MCF547X V4ECORE MMU FPU RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MCF5473 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MCF547x Integrated Microprocessor Electrical Characteristics |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。