- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45312 > MCF54454VR266 (FREESCALE SEMICONDUCTOR INC) 32-BIT, 266 MHz, RISC PROCESSOR, PBGA360 PDF資料下載

參數(shù)資料

| 型號(hào): | MCF54454VR266 |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA360 |

| 封裝: | 23 X 23 MM, ROHS COMPLIANT, TEPBGA-360 |

| 文件頁數(shù): | 16/48頁 |

| 文件大?。?/td> | 945K |

| 代理商: | MCF54454VR266 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

Electrical Characteristics

MCF5445x ColdFire Microprocessor Data Sheet, Rev. 6

Freescale Semiconductor

23

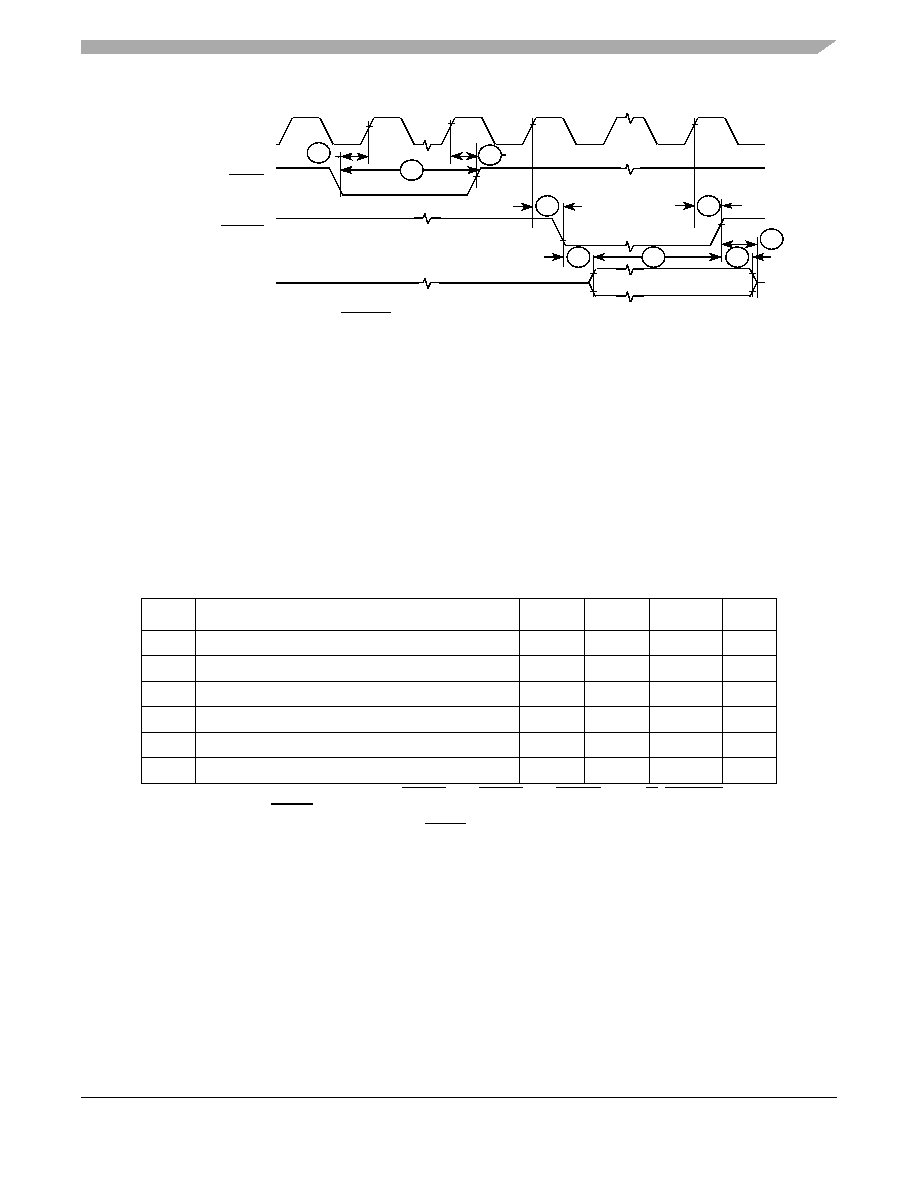

Figure 8. RESET and Configuration Override Timing

5.7

FlexBus Timing Specifications

A multi-function external bus interface called FlexBus is provided with basic functionality to interface to slave-only devices up

to a maximum bus frequency of 66MHz. It can be directly connected to asynchronous or synchronous devices such as external

boot ROMs, flash memories, gate-array logic, or other simple target (slave) devices with little or no additional circuitry. For

asynchronous devices, a simple chip-select based interface can be used.

All processor bus timings are synchronous; input setup/hold and output delay are given in respect to the rising edge of a

reference clock, FB_CLK. The FB_CLK frequency may be the same as the internal system bus frequency or an integer divider

of that frequency.

The following timing numbers indicate when data is latched or driven onto the external bus, relative to the Flexbus output clock

(FB_CLK). All other timing relationships can be derived from these values.

NOTE

The processor drives the data lines during the first clock cycle of the transfer

with the full 32-bit address. This may be ignored by standard connected

devices using non-multiplexed address and data buses. However, some

applications may find this feature beneficial.

The address and data busses are muxed between the FlexBus and PCI

controller. At the end of the read and write bus cycles the address signals are

indeterminate.

Table 12. FlexBus AC Timing Specifications

Num

Characteristic

Min

Max

Unit

Notes

Frequency of Operation

25

66.66

MHz

FB1

Clock Period

15

40

ns

FB2

Output Valid

—

7.0

ns

1

1 Specification is valid for all FB_AD[31:0], FB_BS[3:0], FB_CS[3:0], FB_OE, FB_R/W, FB_TBST,

FB_TSIZ[1:0], and FB_TS.

FB3

Output Hold

1.0

—

ns

1

FB4

Input Setup

3.0

—

ns

2

2 Specification is valid for all FB_AD[31:0] and FB_TA.

FB5

Input Hold

0

—

ns

2

R1

R2

CLKIN

RESET

RSTOUT

R3

R4

R8

R7

R6

R5

Configuration Overrides*:

R4

(BOOTMOD[1:0],

Override pins])

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCF54451CVM180 | 32-BIT, 180 MHz, RISC PROCESSOR, PBGA256 |

| MCF54455VR266 | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA360 |

| MCF54451VM240 | 32-BIT, 240 MHz, RISC PROCESSOR, PBGA256 |

| MCF54452CVR200 | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA360 |

| MCF5471ZP200 | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA388 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCF54455 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ColdFire㈢ Microprocessor |

| MCF54455_08 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ColdFire㈢ Microprocessor |

| MCF54455_0812 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MCF5445x ColdFire?? Microprocessor Data Sheet |

| MCF54455_09 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MCF5445x ColdFire?? Microprocessor Data Sheet |

| MCF54455ACVR200 | 制造商:Freescale Semiconductor 功能描述:MCF5445X RISC 32-BIT 200MHZ 1.8V/2.5V/3.3V 360-PIN TEBGA TRA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。