- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄44572 > LM79CCVFX (NATIONAL SEMICONDUCTOR CORP) SPECIALTY ANALOG CIRCUIT, PQFP44 PDF資料下載

參數(shù)資料

| 型號: | LM79CCVFX |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 模擬信號調(diào)理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PQFP44 |

| 封裝: | 10 X 10 MM, PLASTIC, QFP-44 |

| 文件頁數(shù): | 20/31頁 |

| 文件大小: | 469K |

| 代理商: | LM79CCVFX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

Functional Description (Continued)

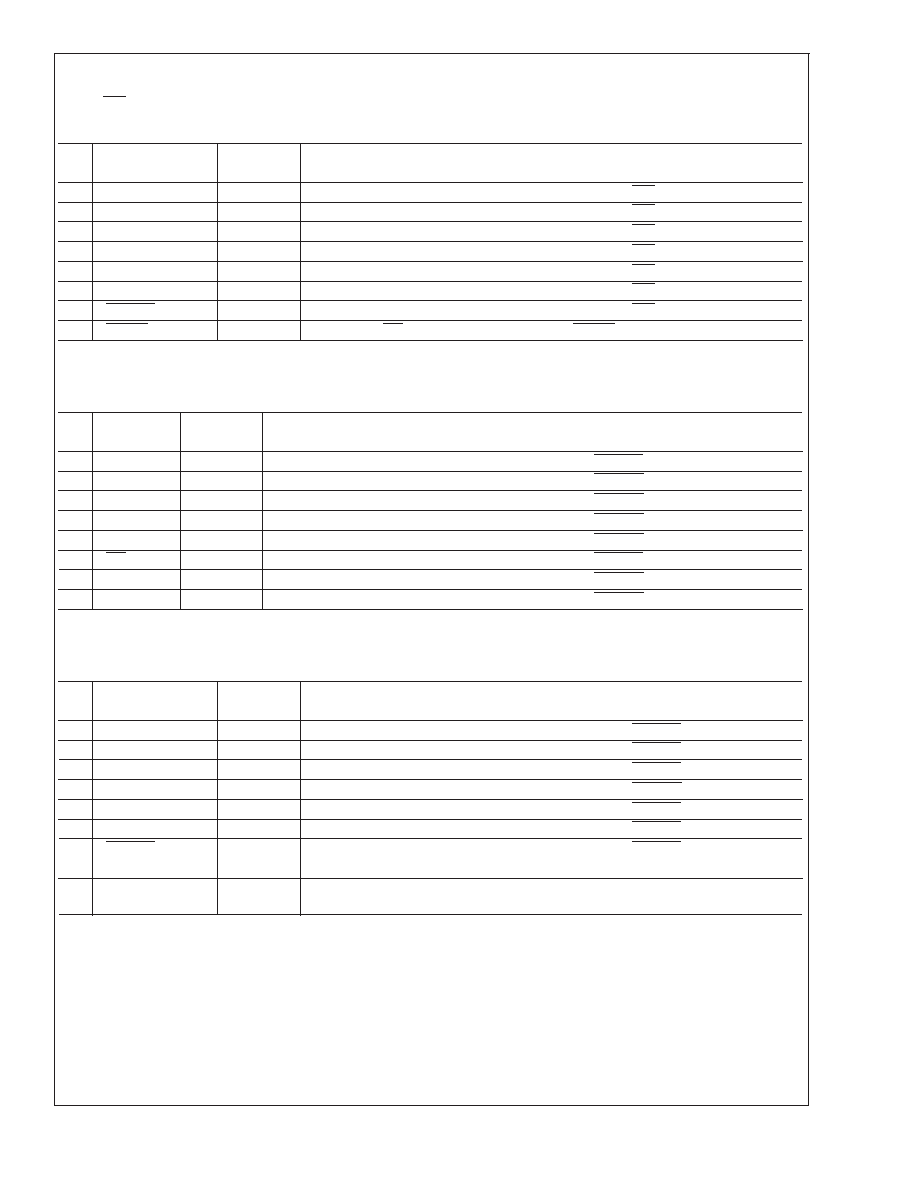

13.7 SMI Mask Register 2 — Address 44h

Power on default <7:0> = 00h

Bit

Name

Read/

Write

Description

0

IN4

Read/Write

A one disables the corresponding interrupt status bit for SMI interrupt.

1

-IN5

Read/Write

A one disables the corresponding interrupt status bit for SMI interrupt.

2

-IN6

Read/Write

A one disables the corresponding interrupt status bit for SMI interrupt.

3

FAN3

Read/Write

A one disables the corresponding interrupt status bit for SMI interrupt.

4

Chassis Intrusion

Read/Write

A one disables the corresponding interrupt status bit for SMI interrupt.

5

FIFO Overflow

Read/Write

A one disables the corresponding interrupt status bit for SMI interrupt.

6

SMI__IN

Read/Write

A one disables the corresponding interrupt status bit for SMI interrupt.

7

RESET Enable

Read/Write

<7> = 1 in SM Mask Register 2 enables the RESET in the Configuration Register.

13.8 NMI Mask Register 1 — Address 45h

Power on default <7:0> = 00h

Bit

Name

Read/

Write

Description

0

IN0

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

1

IN1

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

2

IN2

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

3

IN3

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

4

Temperature

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

5

BTI

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

6

FAN1

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

7

FAN2

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

13.9 NMI Mask Register 2 — Address 46h

Power on <7:0> = 01000000 binary

Bit

Name

Read/

Write

Description

0

IN4

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

1

-IN5

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

2

-IN6

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

3

FAN3

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

4

Chassis Intrusion

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

5

FIFO Overflow

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

6

SMI__IN

Read/Write

A one disables the corresponding interrupt status bit for NMI/IRQ interrupt.

Note: The Power on default is 1 for this bit.

7

Chassis Clear

Read/Write

A one outputs a minimum 20 ms active low pulse on the Chassis Intrusion pin. The

register bit self clears after the pulse has been output.

LM79

www.national.com

27

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM86BIMQX | SPECIALTY ANALOG CIRCUIT, PDSO24 |

| LM85BIMQ/NOPB | SPECIALTY ANALOG CIRCUIT, PDSO24 |

| LM9140BYZ-5.0X | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, 5 V, PBCY3 |

| LM9140BYZ-4.1X | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, 4.096 V, PBCY3 |

| LM9140BYZ-5.0 | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, 5 V, PBCY3 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM79GCP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Negative Adjustable Voltage Regulator |

| LM79L | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:3-Terminal Negative Regulators |

| LM79L00 | 制造商:FCI 制造商全稱:First Components International 功能描述:LM79L00 Series 3-Terminal Negative Output voltage Regulators |

| LM79L05 | 制造商:KEXIN 制造商全稱:Guangdong Kexin Industrial Co.,Ltd 功能描述:Three-terminal negative voltage regulator |

| LM79L05A | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:3-Terminal 0.1A Negative Voltage Regulator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。