- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384544 > ISPCLOCK5600 (Lattice Semiconductor Corporation) In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer PDF資料下載

參數(shù)資料

| 型號: | ISPCLOCK5600 |

| 廠商: | Lattice Semiconductor Corporation |

| 英文描述: | In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| 中文描述: | 在系統(tǒng)可編程,零延遲時(shí)鐘發(fā)生器通用扇出緩沖器 |

| 文件頁數(shù): | 33/47頁 |

| 文件大小: | 871K |

| 代理商: | ISPCLOCK5600 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當(dāng)前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

Lattice Semiconductor

ispClock5600 Family Data Sheet

33

User Electronic Signature

A user electronic signature (UES) feature is included in the E

2

CMOS memory of the ispClock5600. This consists of

32 bits that can be con

fi

gured by the user to store unique data such as ID codes, revision numbers or inventory

control data. The speci

fi

cs this feature are discussed in the IEEE 1149.1 serial interface section of this data sheet.

Electronic Security

An electronic security “fuse” (ESF) bit is provided in every ispClock5600 device to prevent unauthorized readout of

the E

2

CMOS con

fi

guration bit patterns. Once programmed, this cell prevents further access to the functional user

bits in the device. This cell can only be erased by reprogramming the device, so the original con

fi

guration can not

be examined once programmed. Usage of this feature is optional. The speci

fi

cs of this feature are discussed in the

IEEE 1149.1 serial interface section of this data sheet.

Production Programming Support

Once a

fi

nal con

fi

guration is determined, an ASCII format JEDEC

fi

le can be created using the PAC-Designer soft-

ware. Devices can then be ordered through the usual supply channels with the user’s speci

fi

c con

fi

guration already

preloaded into the devices. By virtue of its standard interface, compatibility is maintained with existing production

programming equipment, giving customers a wide degree of freedom and

fl

exibility in production planning.

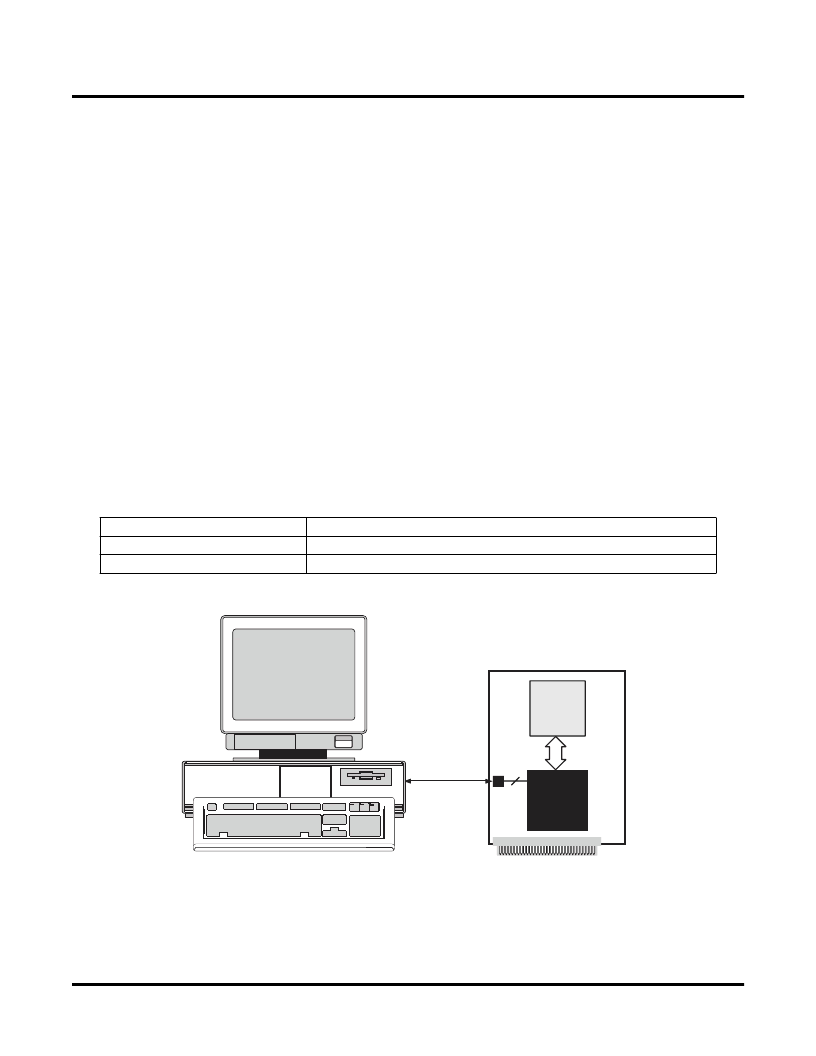

Evaluation Fixture

Included in the basic ispClock5600 Design Kit is an engineering prototype board that can be connected to the par-

allel port of a PC using a Lattice ispDOWNLOAD

cable. It demonstrates proper layout techniques for the

ispClock5600 and can be used in real time to check circuit operation as part of the design process. Input and out-

put connections (SMA connectors for all RF signals) are provided to aid in the evaluation of the ispClock5600 for a

given application. (Figure 29).

Figure 29. Download from a PC

Part Number

Description

PAC-SYSTEMCLK5620

Complete system kit, evaluation board, ispDOWNLOAD cable and software.

PACCLK5620-EV

Evaluation board only, with components, fully assembled.

ispDownload

Cable (6')

4

Other

System

Circuitry

ispClock5600

Device

PAC-Designer

Software

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISPPAC-CLK5610V-01T100C | In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| ISPPAC-CLK5620V-01T100C | LED Area Light; LED Color:Blue; Leaded Process Compatible:No; Light Emitting Area:80x80mm; Peak Reflow Compatible (260 C):No; Supply Current:250mA; Supply Voltage:24VDC; Wavelength:470nm |

| ISPPAC-CLK5620V-01T100I | In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| ISPPAC-CLK5610V-01T48C | Spot Light; LED Color:Blue; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No; Supply Current:160mA; Supply Voltage:30VDC; Wavelength:470nm |

| ISPPAC-CLK5620V-01T48C | LED Area Light; LED Color:Green; Leaded Process Compatible:No; Light Emitting Area:62x62mm; Peak Reflow Compatible (260 C):No; Supply Current:200mA; Supply Voltage:24VDC; Wavelength:525nm |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISPCLOCK5600A | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable, Enhanced Zero-Delay, Clock Generator with Universal Fan-Out Buffer |

| ISPCLOCK5610A | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable, Enhanced Zero-Delay, Clock Generator with Universal Fan-Out Buffer |

| ISPCLOCK5620A | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable, Enhanced Zero-Delay, Clock Generator with Universal Fan-Out Buffer |

| ISPD60 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DARLINGTON-NPN-OUTPUT DC-INPUT OPTOCOUPLER |

| ISPD60_10 | 制造商:ISOCOM 制造商全稱:ISOCOM 功能描述:NON BASE LEAD OPTICALLY COUPLED ISOLATOR PHOTODARLINGTON OUTPUT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。