- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385407 > HT9580 (Holtek Semiconductor Inc.) Character Pager Controller PDF資料下載

參數(shù)資料

| 型號: | HT9580 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | Character Pager Controller |

| 中文描述: | 字符傳呼機控制器 |

| 文件頁數(shù): | 17/63頁 |

| 文件大小: | 444K |

| 代理商: | HT9580 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁

HT9580

17

April 28, 2000

Preliminary

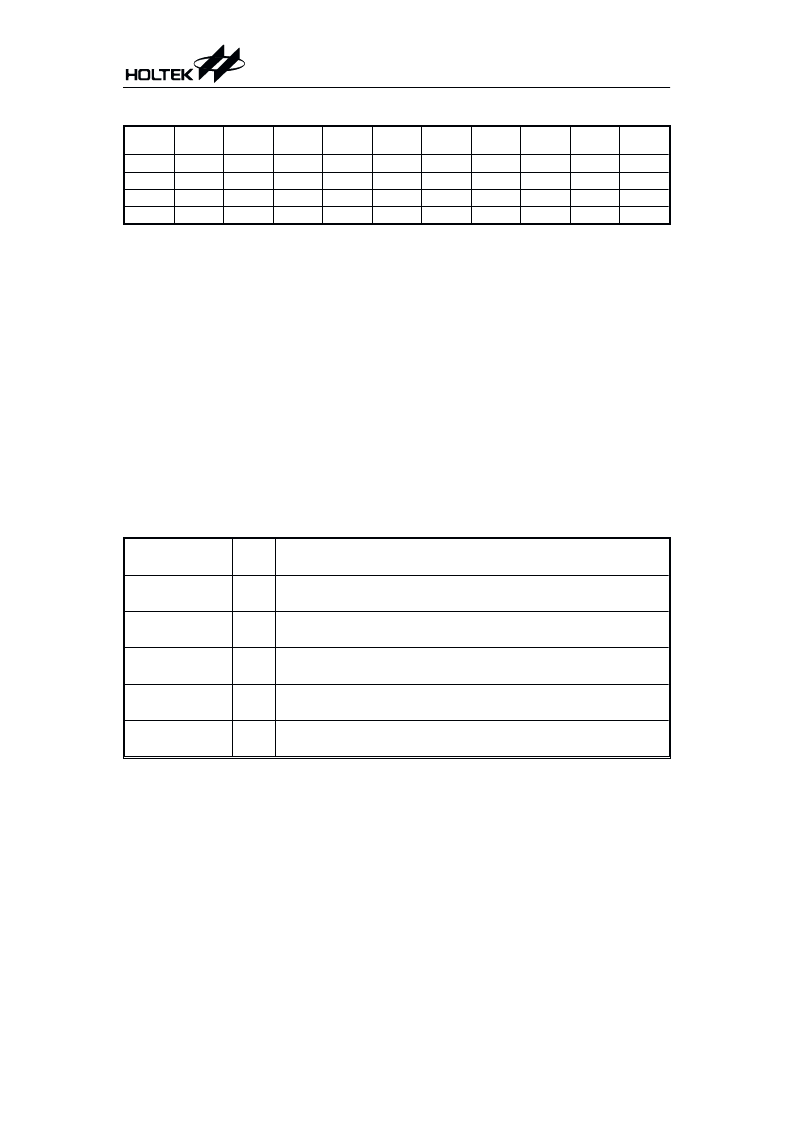

Timer registers

Address

Register

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

State on

POR

0007H

TMRC

TMR1MOD

X

TMR1CLK

TMR0CLK

TMR1EDG

TMR0EDG

TMR1EN

TMR0EN

0u00 0000

0008H

TMR1L

TM1D7

TM1D6

TM1D5

TM1D4

TM1D3

TM1D2

TM1D1

TM1D0

uuuu uuuu

0009H

TMR1H

TM1D15

TM1D14

TM1D13

TM1D12

TM1D11

TM1D10

TM1D9

TM1D8

uuuu uuuu

000AH

TMR0

TM0D7

TM0D6

TM0D5

TM0D4

TM0D3

TM0D2

TM0D1

TM0D0

uuuu uuuu

In addition to the watchdog timer, the HT9580

provides two timers: an 8-bit timer (timer 0) and

one 16-bit timer (timer 1). Those two timers are

controlled and configured by the register TMRC.

Both timers are programmable up-count coun-

ters whose clocks may be derived from the

X1-clock (32.768kHz, 76.8kHz or 153.6kHz). To

program the timers, TMR0, TMR1L, and

TMR1H should be written with a start value.

When the timers are enabled, they will count-up

from the start value. If the timers overflow, cor-

responding interrupts will be generated. When

the timers are disabled, the counter contents

will not be reset. To reset the counter contents,

the software should write the start value again.

Since timer1 is a 16-bit counter, it is important

to note the method of writing data to both

TMR1L and TMR1H. Writing to TMR1L only

writesthedataintoalowbytebuffer,whilewrit-

ing to TMR1H will simultaneously write the

high byte data and the contents of the low byte

buffer into the Timer Counter preload register

(16-bit). Note that the Timer counter preload

register contents are changed by a TMR1H

write operation while writing to TMR1L does

not change the contents of the preload register.

Reading TMR1H will also latch the contents of

TMR1L into the byte buffer to avoid false timing

problem. Reading TMR1L returns the contents

of the low byte buffer. In other words, the low

byteofthetimercountercannotbereaddirectly.

It must first read TMR1H to latch the low byte

contents of the timer counter into the buffer.

TMRC is the timer counter control register,

which defines the timer counter options. The

timer1 clock source can be selected from either

theinternalclockoranexternalinputclockbybit

TMR1MOD of the TMRC register. The

timer0/timer1 can also select its clock source by

bits TMR0CLK/TMR1CLK. TMRC as shown in

the table.

Labels (TMRC0

and TMRC1)

Bits

Function

TMR0EN,

TMR1EN

0

1

Enable/disable timer counting

(0=disable; 1=enable)

TMR0EDG,

TMR1EDG

2

3

Define the TMR0 and TMR1 active edge

(0=active on low to high; 1=active on high to low)

TMR0CLK

4

Select TMR0 clock source

(0=X1-clock; 1=OSC1 input clock/system clock)

TMR1CLK

5

Select TMR1 clock source if internal clock input is selected

(0=X1-clock; 1=OSC1 input clock/system clock)

TMR1MOD

7

Define the TMR1 operation mode

(0=internal clock input; 1=external clock input)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT95A30P | 8-Bit LCD Type Phone Controller MCU |

| HT95L300 | 8-Bit LCD Type Phone Controller MCU |

| HT95A20P | 8-Bit LCD Type Phone Controller MCU |

| HT95L300-100QEP-A | LCD Type Phone 8-Bit MCU |

| HT95A400 | Time-Delay Relay; Mounting Type:Plug In; Relay Mounting:Plug-In |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT95A100 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:LCD Type Phone 8-Bit MCU |

| HT95A100/10P | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:I/O Type Phone 8-Bit MCU |

| HT95A10P | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:LCD Type Phone 8-Bit MCU |

| HT95A200 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:I/O Type Phone 8-Bit MCU |

| HT95A200/20P | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:I/O Type Phone 8-Bit MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。