- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385396 > HSP50110JI-52 (HARRIS SEMICONDUCTOR) Digital Quadrature Tuner PDF資料下載

參數(shù)資料

| 型號: | HSP50110JI-52 |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Digital Quadrature Tuner |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQCC84 |

| 文件頁數(shù): | 12/24頁 |

| 文件大小: | 199K |

| 代理商: | HSP50110JI-52 |

3-240

CLK by a programmable factor of 2, 4, or 8. When the

programmable clock factor is 1, IOUT9 is pulled high, and the

CLK signal should be used as the clock. The beginning of a

serial data word is signaled by the assertion of DATARDY one

serial clock before the first bit of the output word. In I followed

by Q Mode, DATARDY is asserted prior to each 16-bit data

word. For added flexibility, the Formatter may be configured to

output the data words in either MSB or LSB first format

.

Gain Distribution

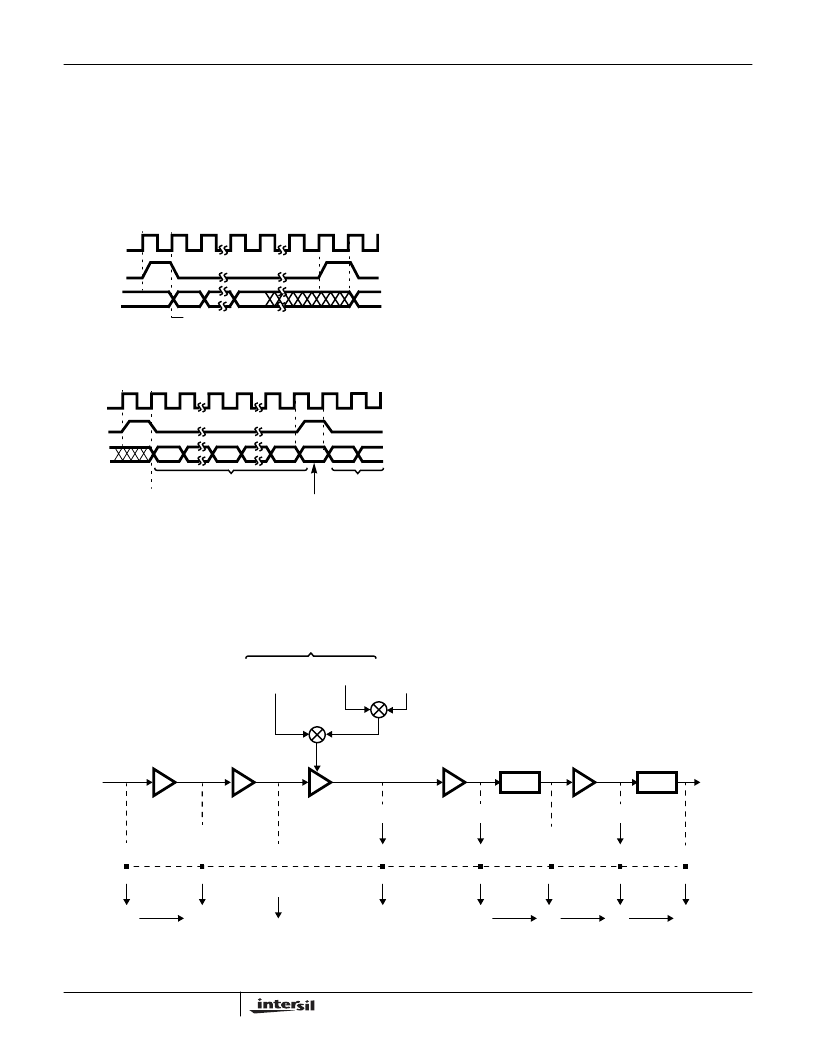

The gain distribution in the DQT is shown in Figure 17. These

gains consist of a combination of fixed, programmable, and

adaptive gains. The fixed gains are introduced by processing

elements like the Synthesizer/Mixer and CIC Filter. The

programmable and adaptive gains are set to compensate for

the fixed gains as well as variations in input signal strength.

The bit range of the data path between processing elements

is shown in Figure 17. The quadrature inputs to the data path

are 10-bit fractional two’s complement numbers. They are

multiplied by a 10-bit quadrature sinusoid and rounded to

12-bits in the Synthesizer/Mixer. The I and Q legs are then

scaled by a fixed gain of 2

-36

to compensate for the worst

case gain of the CIC filter. Next, a gain block with an adaptive

and programmable component is used to set the output signal

level within the desired range of the 10-bit output (see Setting

DQT Gains Section). The adaptive component is produced by

the AGC and has a gain range from 1.0 to 1.9375*2

7

. The

programmable component sets the gain range of the CIC

shifter which may range from 2

0

to 2

63

. Care must be taken

when setting the AGC gain limits and the CIC Shifter gain

since the sum of these gains could shift the CIC Scaler output

beyond the bit range (-2

8

to 2

-46

) of the CIC Filter input. The

CIC Filter introduces a gain factor given by R

N

where R is the

decimation rate of the filter and N is the CIC order. The CIC

order is either 1 (integrate and dump filter) or 3. Depending on

configuration, the CIC Filter introduces a gain factor from 2

0

to

2

36

. The output of the CIC Filter is then rounded and limited to

an 11-bit window between bit positions 2

1

to 2

-9

. Values

outside this range saturate to these 11 bits. The

Compensation Filter introduces a final gain factor of 1.0, 0.65,

LSB

MSB

LSB

IOUT9

IOUT0/

QOUT0

DATARDY

NOTE: Assumes data is being output LSB first.

FIGURE 15. SERIAL TIMING (SIMULTANEOUS I/Q MODE)

DATARDY LEADS 1st BIT

LSB

MSB

0

IOUT9

IOUT0

DATARDY

1

I DATA WORD

MSB

Q DATA

WORD

I OUTPUT IDENTIFIED

BY 1 IN LSB OF DATA WORD

NOTE: Assumes data is being output MSB first.

DATARDY may be programmed active high or low.

FIGURE 16. SERIAL TIMING (I FOLLOWED BY Q MODE)

DATARDY

LEADS 1st BIT

FIGURE 17. GAIN DISTRIBUTION AND INTERMEDIATE BIT WEIGHTINGS

SYNTHESIZER/

MIXER

G = 0.9990

-2

0

2

-9

2

-1

2

0

2

-10

RND

2

-1

-2

1

CIC

G = 2

-36

MANTISSA

1.0 - 1.9375

(0.0625 STEPS)

EXPONENT

2

0

-2

7

SCALER

CIC BARREL

SHIFTER

2

-2

G = 1.0 - 1.9375*2

70

CIC

FILTER

G = 2

0

- 2

36

COMPENSATION

FILTER

GAIN

G = 1.0, 0.65, 0.77

(BYPASS, x/sin(x), (x/sin(x))

3

2

-46

-2

-35

2

0

2

-46

RND

2

-1

-2

8

2

0

2

-9

RND

2

-1

-2

8

2

0

2

-9

2

-1

-2

1

2

0

2

-9

RND

2

-1

-2

3

-2

0

2

-9

2

-1

BINARY POINT

AGC GAIN

INPUT

OUTPUT

BIT RANGE OF DATA PATH

LIMIT

LIMIT

(R

N

)

G

dB

= 0dB

G

dB

= -216.74dB

G

dB

= G

AGC

+

G

SHIFTER

G

dB

= 20log[f

S

/f

D

]

N

= 20log[R]

N

N = 1, 3

G

dB

= 0dB

G

dB

= 0dB

0dB BYPASS

-3.74dB

-2.27dB

G

dB

=

G = -6.02dB

HSP50110

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSP50110JC-52 | CONN HEADER HM 2MM 100POS |

| HSP50110 | Digital Quadrature Tuner(數(shù)字調(diào)諧器) |

| HSP50210 | Digital Costas Loop(數(shù)字Costas鎖相環(huán)) |

| HSP50214VC | Programmable Downconverter |

| HSP50214VI | Programmable Downconverter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP50110JI-52Z | 制造商:Intersil Corporation 功能描述:PB-FREE W/ANNEAL DIGITAL QUADRATURE TUNER 84 PLCC,52MHZ,INDU - Rail/Tube |

| HSP50210 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Digital Costas Loop |

| HSP50210JC-52 | 功能描述:上下轉(zhuǎn)換器 COSTAS DEMODULATOR,84 PLCC,52MHZ,COMM RoHS:否 制造商:Texas Instruments 產(chǎn)品:Down Converters 射頻:52 MHz to 78 MHz 中頻:300 MHz LO頻率: 功率增益: P1dB: 工作電源電壓:1.8 V, 3.3 V 工作電源電流:120 mA 最大功率耗散:1 W 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PQFP-128 |

| HSP50210JC-52Z | 功能描述:上下轉(zhuǎn)換器 COSTAS DEMODULATOR 84 PLCC 52MHZ COM RoHS:否 制造商:Texas Instruments 產(chǎn)品:Down Converters 射頻:52 MHz to 78 MHz 中頻:300 MHz LO頻率: 功率增益: P1dB: 工作電源電壓:1.8 V, 3.3 V 工作電源電流:120 mA 最大功率耗散:1 W 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PQFP-128 |

| HSP50210JI-52 | 功能描述:上下轉(zhuǎn)換器 COSTAS DEMODULATOR,84 PLCC,52MHZ,IND RoHS:否 制造商:Texas Instruments 產(chǎn)品:Down Converters 射頻:52 MHz to 78 MHz 中頻:300 MHz LO頻率: 功率增益: P1dB: 工作電源電壓:1.8 V, 3.3 V 工作電源電流:120 mA 最大功率耗散:1 W 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PQFP-128 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。