- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376630 > DDX4100ERRATA DDX4100 Errata January 17 2002 PDF資料下載

參數(shù)資料

| 型號: | DDX4100ERRATA |

| 英文描述: | DDX4100 Errata January 17 2002 |

| 中文描述: | DDX4100勘誤表02年1月17日 |

| 文件頁數(shù): | 6/27頁 |

| 文件大小: | 1737K |

| 代理商: | DDX4100ERRATA |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

DDX-4100

Regs. 7Ch and 7Eh:

These are the Vendor ID1 and ID2 registers. Any write request to one of these will be ignored.

Regs. 28h:

The

‘Extended Audio ID Register’

is read only. Therefore, any write request will be ignored.

Regs. 26h:

When a write request is issued the actual data written into the RAM register is

“xxxxxxxxxxxx1110’, where ‘x’ represents the incoming data.

Regs. 2Ah:

When a write request is issued the actual data written into the RAM register is

‘xxxxxx0111xxxxxx’, where ‘x’ represents the incoming data.

Regs. 32h and 34h:

Any write request into one of these

sample rate registers

will result in the value BB80h written into

the corresponding RAM register.

3.0 I

2

S INPUT INTERFACE CONFIGURATION

To configure the I

2

S input interface the

Configuration Register B (CRB)

is used. Using the three

I2S1_Align_x bits, one of the seven configuration modes can be selected. Table 2 describes each of

them.

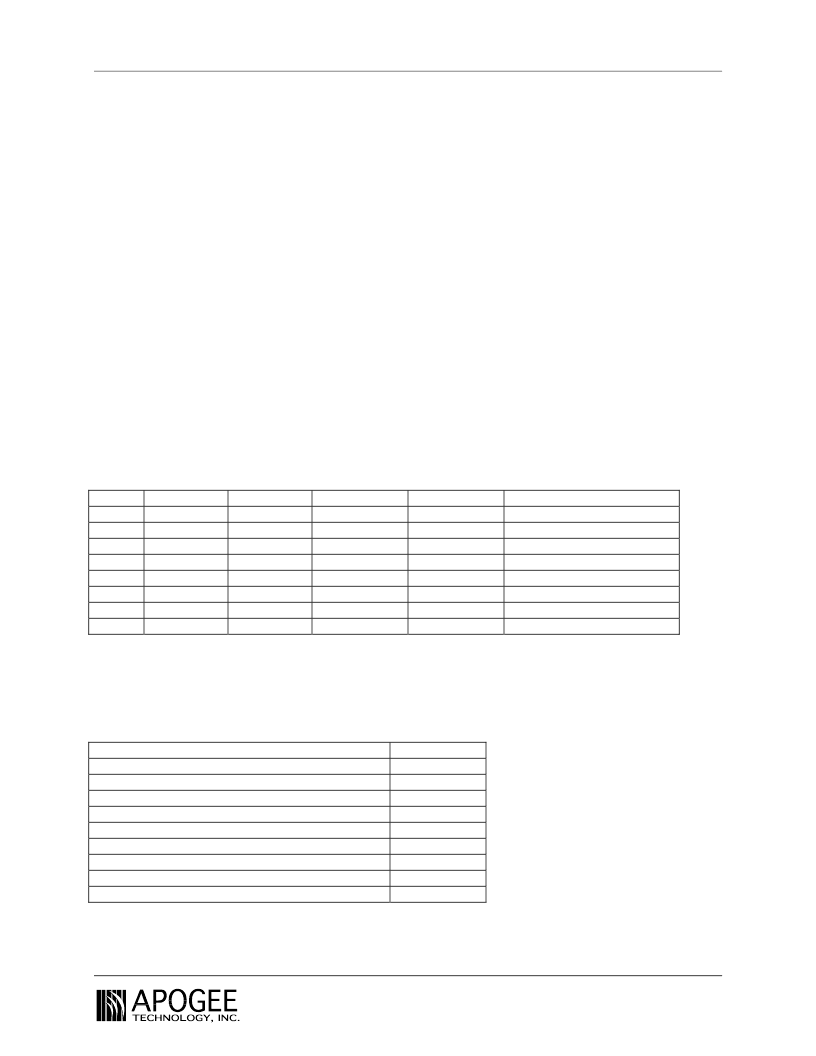

Table 2

Mode

# of Slots

W. Length

Alignment

0

32

24

Left

1

32

24

Left

2

32

16

Right

3

32

24

Right

4

24

24

Left

5

Not Valid

Not Valid

Not Valid

6

24

16

Right

7

24

24

Right

By default the standard I

2

S input interface slave is provided (mode 1 in bits D0, D1,and D2 of register

CRB, I2SS_BICK_POL = 1 and I2SI_LRCK_Pol = 0)

3.0 I

2

S Input switching characteristics (10pF load, Fsm = 32 to 96kHz)

Refer to Figure 1.

BICKI FREQUENCY (master mode)

BICKI FREQUENCY (slave mode)

BICKI pulse width low (T0) (slave mode)

BICKI pulse width high (T0) (slave mode)

BICKI active to LRCKI edge delay (T2)

BICKI active to LRCKI edge delay (T3)

SDI valid to BICKI active setup (T4)

BICKI active to SDI hold time (T5)

BICKI falling to LRCKI edge (T6) (master mode)

BICKI falling to LRCKI edge (T6) (master mode)

Delay Slot

No

Yes

No

No

No

Not Valid

No

No

Notes

MSb first only

Slave only

Reserved, do not use

MSb first only. Slave only

Slave only

3.072MHz

6.4MHz max.

40ns min.

40ns min.

20ns min.

20ns min.

20ns min.

20ns min.

3ns min.

9ns max.

6

Details and Specifications are subject to change without notice

相關PDF資料 |

PDF描述 |

|---|---|

| DDY-EJE-T2 | LED Colored Resin |

| DDY-EJE-T2U-1 | LED Colored Resin |

| DDY-EJE-U1 | LED Colored Resin |

| DDY-EJE-U2 | LED Colored Resin |

| DDY-EJE-UV2-1 | LED Colored Resin |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| DDX-50P-K87 | 制造商:ITT Interconnect Solutions 功能描述:DDX-50P-K87 / 121551-1664 / D Sub |

| DDX-50S-0L2-A197-146 | 制造商:ITT Interconnect Solutions 功能描述:DDX-50S-0L2-A197-146 / 121551-0013 / D SUB |

| DDX-50S-A191-A197 | 制造商:ITT Interconnect Solutions 功能描述:DDX-50S-A191-A197 / 121551-1804 / D Sub |

| DDX8000-TRAY | 制造商:APOGEE TECHNOLOGY 功能描述:DDX 8 Channel Damped Ternary Controller |

| DDX8001-13TR | 制造商:APOGEE TECHNOLOGY 功能描述:DDX 8 Channel Damped Ternary Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復。