- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄376630 > DDX4100ERRATA DDX4100 Errata January 17 2002 PDF資料下載

參數(shù)資料

| 型號(hào): | DDX4100ERRATA |

| 英文描述: | DDX4100 Errata January 17 2002 |

| 中文描述: | DDX4100勘誤表02年1月17日 |

| 文件頁(yè)數(shù): | 20/27頁(yè) |

| 文件大小: | 1737K |

| 代理商: | DDX4100ERRATA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

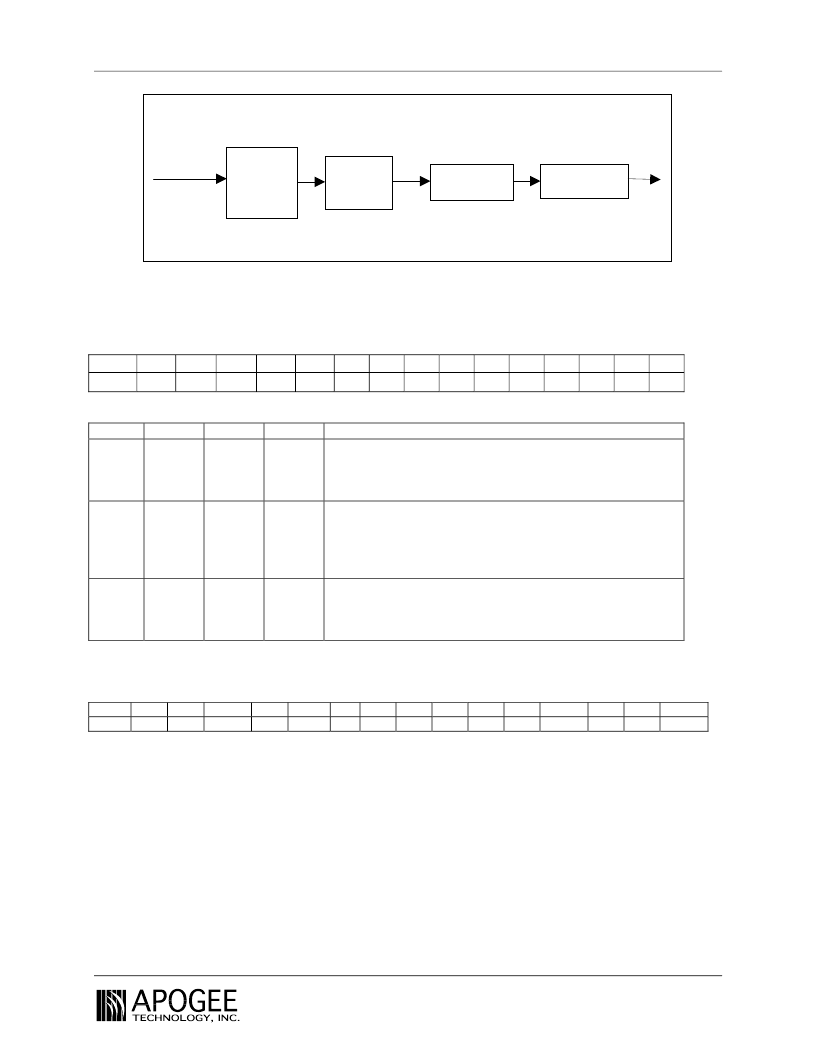

DDX-4100

Volume

Biquads

Pre-

Scale

Bass

/

Treble

Figure 11: Digital Audio Signal Flow

12.4 Power-down Ctrl/Status Register (PCSR) (address 26h)

D15

D14 D13

D12 D11 D10

EAPD

PR5 PR4

BIT

R/W

RST

NAME

D12

R/W

0

PR4

D9

D8

D7

D6

D5

D4

D3

1

D2

1

D1

1

D0

0

DESCRIPTION

Setting this bit to 1 the BIT_Clk and the SDATA_IN signal

will be fixed to the digital low level. To resume the normal

operation either a hardware reset or a

softReset

must be

performed.

In order to set the device in a power-down-like condition

this bit must be set to 1. This will stop the device internal

clock: only the PL and AC’97, I

C clocks will still be

running. The DSP starts the power-down sequence

(volume fade-out and MUTE).

The value of this bit is checked by the DSP in order to

recognize an external power amplifier power-down

request. As a consequence the DSP starts the power-

down sequence (volume fade-out and MUTE).

D13

R/W

0

PR5

D15

R/W

1

EAPD

NOTE: Bit D0, D3 will be masked to show the value before writing into the RAM register, other bits will simply pass through

.

12.5

Extended Audio ID Register (address 28h) AC’97 Only

D15

D14

D13

D12

D11

D10

D9

D8

0

ID0

0

0

0

0

0

1

The Extended Audio ID is a read-only register that identifies which extended audio features are supported

(see AC’97 revision 2.1 specification, section A2.1). The extended features supported are Variable Rate

PCM Audio (VRA), Double rate PCM Audio (DRA), PCM Center (CDAC), PCM Surround (SDAC) and

PCM LFE (LDAC).

Code ID0, at D14, reports the status of the SA pin. Code ID1, at D15, always reports 0. Hence, the

configurations are primary (00) if SA pin is 0 or Secondary (01) if SA pin is 1.

D7

1

D6

1

D5

0

D4

0

D3

0

D2

0

D1

1

D0

1

20

Details and Specifications are subject to change without notice

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DDY-EJE-T2 | LED Colored Resin |

| DDY-EJE-T2U-1 | LED Colored Resin |

| DDY-EJE-U1 | LED Colored Resin |

| DDY-EJE-U2 | LED Colored Resin |

| DDY-EJE-UV2-1 | LED Colored Resin |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DDX-50P-K87 | 制造商:ITT Interconnect Solutions 功能描述:DDX-50P-K87 / 121551-1664 / D Sub |

| DDX-50S-0L2-A197-146 | 制造商:ITT Interconnect Solutions 功能描述:DDX-50S-0L2-A197-146 / 121551-0013 / D SUB |

| DDX-50S-A191-A197 | 制造商:ITT Interconnect Solutions 功能描述:DDX-50S-A191-A197 / 121551-1804 / D Sub |

| DDX8000-TRAY | 制造商:APOGEE TECHNOLOGY 功能描述:DDX 8 Channel Damped Ternary Controller |

| DDX8001-13TR | 制造商:APOGEE TECHNOLOGY 功能描述:DDX 8 Channel Damped Ternary Controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。