- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1991 > CS4362-KQZ (Cirrus Logic Inc)IC DAC 6CH 114DB 192KHZ 48LQFP PDF資料下載

參數(shù)資料

| 型號: | CS4362-KQZ |

| 廠商: | Cirrus Logic Inc |

| 文件頁數(shù): | 3/42頁 |

| 文件大小: | 0K |

| 描述: | IC DAC 6CH 114DB 192KHZ 48LQFP |

| 標準包裝: | 250 |

| 位數(shù): | 24 |

| 數(shù)據(jù)接口: | 串行 |

| 轉(zhuǎn)換器數(shù)目: | 6 |

| 電壓電源: | 模擬和數(shù)字 |

| 功率耗散(最大): | 390mW |

| 工作溫度: | -10°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 48-LQFP |

| 供應商設備封裝: | 48-LQFP(7x7) |

| 包裝: | 托盤 |

| 輸出數(shù)目和類型: | 6 電壓,單極 |

| 采樣率(每秒): | 200k |

| 產(chǎn)品目錄頁面: | 757 (CN2011-ZH PDF) |

| 其它名稱: | 598-1644 |

第1頁第2頁當前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

DS257F2

11

CS4362

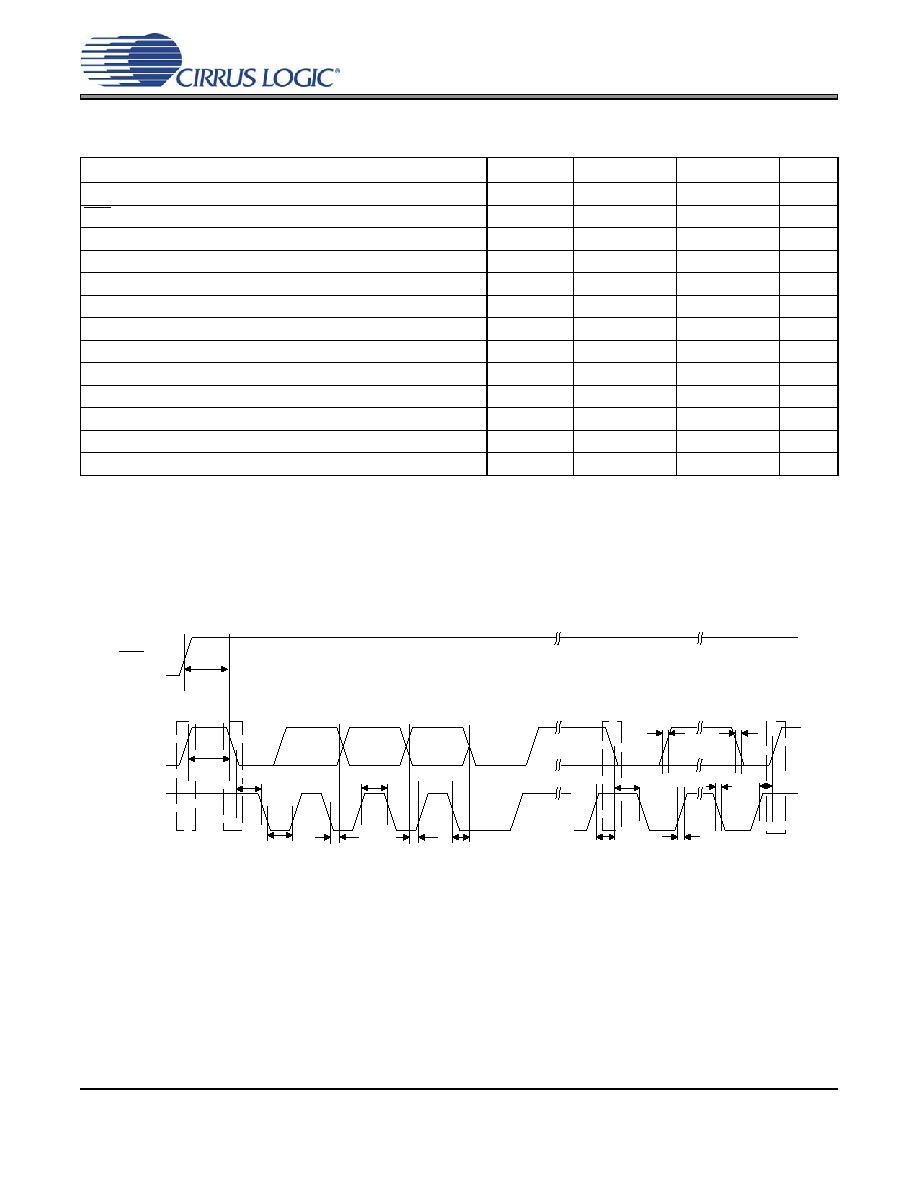

SWITCHING CHARACTERISTICS - CONTROL PORT - IC FORMAT

(For KQZ TA = -10°C to +70°C; VLC = 1.8 V to 5.5 V; Inputs: Logic 0 = GND, Logic 1 = VLC, CL =30pF)

Notes:

19. Data must be held for sufficient time to bridge the transition time, tfc, of SCL.

20. The acknowledge delay is based on MCLK and can limit the maximum transaction speed.

21.

for Single-Speed Mode,

for Double-Speed Mode,

for Quad-Speed Mode.

Parameter

Symbol

Min

Max

Unit

SCL Clock Frequency

fscl

-

100

kHz

RST Rising Edge to Start

tirs

500

-

ns

Bus Free Time Between Transmissions

tbuf

4.7

-

s

Start Condition Hold Time (prior to first clock pulse)

thdst

4.0

-

s

Clock Low time

tlow

4.7

-

s

Clock High Time

thigh

4.0

-

s

Setup Time for Repeated Start Condition

tsust

4.7

-

s

SDA Hold Time from SCL Falling

thdd

0-

s

SDA Setup time to SCL Rising

tsud

250

-

ns

Rise Time of SCL and SDA

trc, trc

-1

s

Fall Time SCL and SDA

tfc, tfc

-

300

ns

Setup Time for Stop Condition

tsusp

4.7

-

s

Acknowledge Delay from SCL Falling

tack

-

ns

15

256

Fs

×

---------------------

15

128

Fs

×

---------------------

15

64

Fs

×

------------------

t buf

t

hdst

t

lo w

t

hdd

t

high

t sud

Stop

S t a rt

SD A

SC L

t

irs

RS T

t

hdst

t

rc

t

fc

t sust

t susp

St a rt

Stop

R epe a t e d

t

rd

t

fd

t ack

Figure 3. Control Port Timing - IC Format

相關PDF資料 |

PDF描述 |

|---|---|

| CS4362A-DQZ | IC DAC 6CH 114DB 192KHZ 48-LQFP |

| CS4364-CQZR | IC DAC 103DB 24BIT 6CH 48-LQFP |

| CS4382A-DQZ | IC DAC 8CH 114DB 192KHZ 48-LQFP |

| CS4384-CQZR | IC DAC 8CH 103DB 192KHZ 48-LQFP |

| CS4385-DQZR | IC DAC 8CH 114DB 192KHZ 48-LQFP |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CS4362-KQZR | 功能描述:數(shù)模轉(zhuǎn)換器- DAC IC 114dB 192kHz 6Ch DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| CS4364 | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:103 dB, 192 kHz 6-Channel D/A Converter |

| CS4364_08 | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:103 dB, 192 kHz 6-Channel D/A Converter |

| CS4364-CQZ | 功能描述:數(shù)模轉(zhuǎn)換器- DAC IC 24bit 6Chn DAC w/ DSD Supt&Lw-Ltnc DF RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| CS4364-CQZR | 功能描述:數(shù)模轉(zhuǎn)換器- DAC IC 24b 6Ch DAC w/DSD Supt/Lw-Ltnc DF RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。