- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379806 > CD40105BMS (Intersil Corporation) CMOS FIFO Register(CMOS 先進(jìn)先出寄存器) PDF資料下載

參數(shù)資料

| 型號(hào): | CD40105BMS |

| 廠商: | Intersil Corporation |

| 英文描述: | CMOS FIFO Register(CMOS 先進(jìn)先出寄存器) |

| 中文描述: | FIFO寄存器的CMOS的CMOS(先進(jìn)先出寄存器) |

| 文件頁(yè)數(shù): | 5/10頁(yè) |

| 文件大小: | 116K |

| 代理商: | CD40105BMS |

7-1321

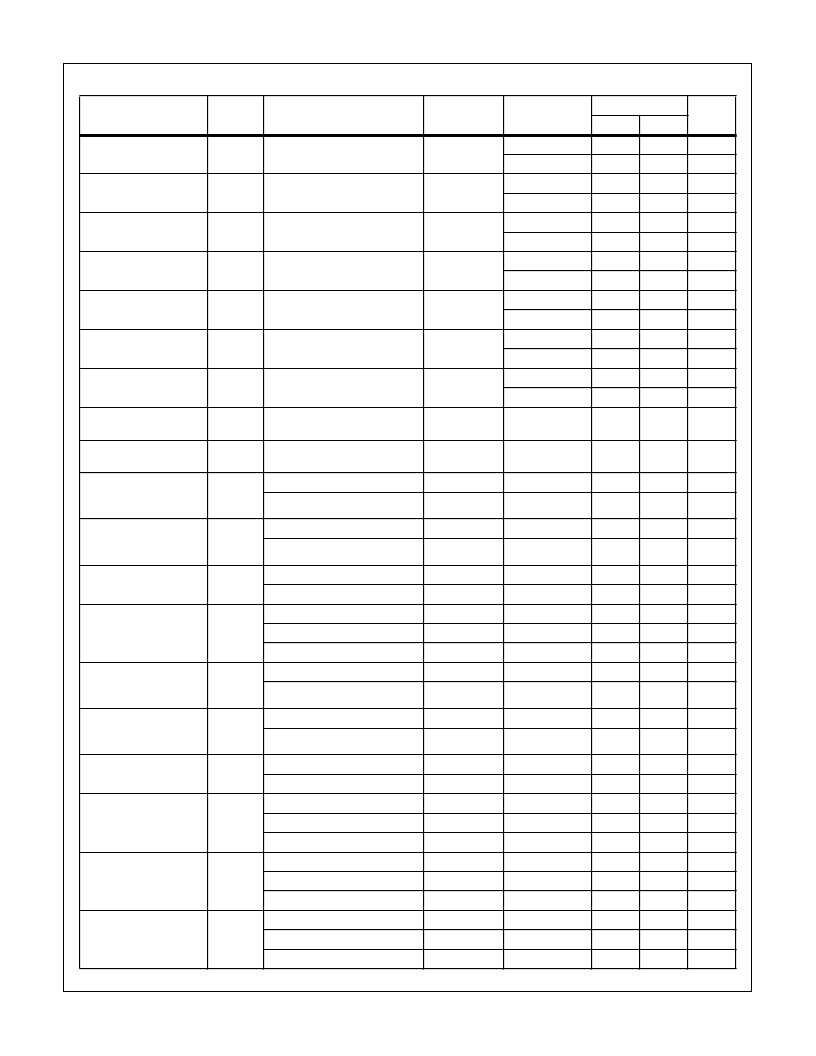

Specifications CD40105BMS

Output Current (Sink)

IOL5

VDD = 5V, VOUT = 0.4V

1, 2

+125

o

C

-55

o

C

+125

o

C

-55

o

C

+125

o

C

-55

o

C

+125

o

C

-55

o

C

+125

o

C

-55

o

C

+125

o

C

-55

o

C

+125

o

C

-55

o

C

0.36

-

mA

0.64

-

mA

Output Current (Sink)

IOL10

VDD = 10V, VOUT = 0.5V

1, 2

0.9

-

mA

1.6

-

mA

Output Current (Sink)

IOL15

VDD = 15V, VOUT = 1.5V

1, 2

2.4

-

mA

4.2

-

mA

Output Current (Source)

IOH5A

VDD = 5V, VOUT = 4.6V

1, 2

-

-0.36

mA

-

-0.64

mA

Output Current (Source)

IOH5B

VDD = 5V, VOUT = 2.5V

1, 2

-

-1.15

mA

-

-2.0

mA

Output Current (Source)

IOH10

VDD = 10V, VOUT = 9.5V

1, 2

-

-0.9

mA

-

-1.6

mA

Output Current (Source)

IOH15

VDD =15V, VOUT = 13.5V

1, 2

-

-2.4

mA

-

-4.2

mA

Input Voltage Low

VIL

VDD = 10V, VOH > 9V, VOL < 1V

1, 2

+25

o

C, +125

o

C,

-55

o

C

+25

o

C, +125

o

C,

-55

o

C

+25

o

C

+25

o

C

-

3

V

Input Voltage High

VIH

VDD = 10V, VOH > 9V, VOL < 1V

1, 2

7

-

V

Propagation Delay

Shift or Reset to Data Out

Ready

TPHL1

VDD = 10V

1, 2, 3

-

180

ns

VDD = 15V

1, 2, 3

-

130

ns

Propagation Delay Ripple

through Delay Input to

Output

TPLH3

VDD = 10V

1, 2, 3

+25

o

C

+25

o

C

-

2

μ

s

VDD = 15V

1, 2, 3

-

1.4

μ

s

Propagation Delay

Shift-In to Data-In Ready

TPHL2

VDD = 10V

1, 2, 3

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

-

130

ns

VDD = 15V

1, 2, 3

-

90

ns

Propagation Delay

Shift Out to QN Out

TPHL4

TPLH4

VDD = 5V

1, 2, 3

-

420

ns

VDD = 10V

1, 2, 3

-

380

ns

VDD = 15V

1, 2, 3

-

250

ns

Propagation Delay

3-State Control to Data

Out

TPZH

TPZL

VDD = 10V

1, 2, 4

-

120

ns

VDD = 15V

1, 2, 4

-

80

ns

Propagation Delay

3-State Control to Data

Out

TTHZ

TPLZ

VDD = 10V

1, 2, 3

+25

o

C

+25

o

C

-

100

ns

VDD = 15V

1, 2, 3

-

80

ns

Maximum Shift-In or

Shift-Out Rate

FCL

VDD = 10V

1, 2

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

3

-

MHz

VDD = 15V

1, 2

4

-

MHz

Maximum Shift-In or

Shift-Out Rise Time

TR

VDD = 5V

3

-

15

μ

s

VDD = 10V

3

-

15

μ

s

VDD = 15V

3

-

15

μ

s

Maximum Shift-In Fall

Time

TF

VDD = 5V

3

-

15

μ

s

VDD = 10V

3

-

15

μ

s

VDD = 15V

3

-

15

μ

s

Maximum Shift-Out Fall

Time

TF

VDD = 5V

3

-

15

μ

s

VDD = 10V

3

-

5

μ

s

VDD = 15V

3

-

5

μ

s

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS (Continued)

PARAMETER

SYMBOL

CONDITIONS

NOTES

TEMPERATURE

LIMITS

UNITS

MIN

MAX

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CD40106BC | Hex Schmitt Trigger(六施密特觸發(fā)器) |

| CD40106BMJ | 16-Bit Transparent D-Type Latch With 3-State Outputs 48-SSOP -40 to 85 |

| CD40106 | CMOS HEX SCHMITT TRIGGERS |

| CD40106BMN | 16-Bit Transparent D-Type Latch With 3-State Outputs 48-SSOP -40 to 85 |

| CD40106 | Hex Schmitt Trigger |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CD40106 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS Hex Schmitt Triggers |

| CD40106_12 | 制造商:UTC-IC 制造商全稱:UTC-IC 功能描述:HEX SCHMITT TRIGGERS |

| CD40106B | 制造商:TI 制造商全稱:Texas Instruments 功能描述:CMOS HEX SCHMITT TRIGGERS |

| CD40106BC | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Hex Schmitt Trigger |

| CD40106BC_03 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Hex Schmitt Trigger |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。