- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373971 > AD9937 (Analog Devices, Inc.) CCD Signal Processor with Precision Timing⑩ Generator PDF資料下載

參數(shù)資料

| 型號: | AD9937 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | CCD Signal Processor with Precision Timing⑩ Generator |

| 中文描述: | CCD信號處理器精確定時⑩發(fā)生器 |

| 文件頁數(shù): | 9/44頁 |

| 文件大小: | 410K |

| 代理商: | AD9937 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

REV. 0

AD9937

–9–

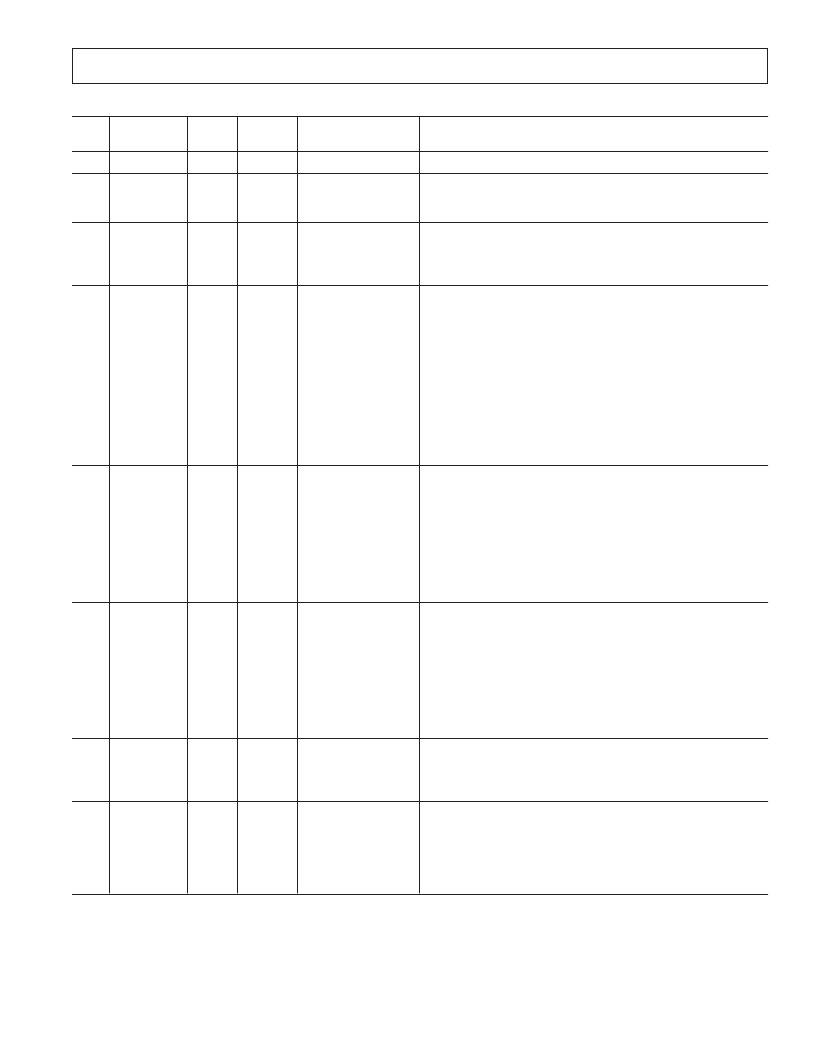

Table I. Control Register Map

Bit

Breakdown Width

Bit

Register

Name

Addr

Default

Function

0

1

(23:0)

0

24

1

0

0

SW_RESET

OUTCONT_REG

Software Reset = 000000 (Reset All Registers to Default).

Internal OUTCONT Signal Control (0 = Digital Outputs held

at fixed dc level, 1 = Normal Operation).

(23:1)

(1:0)

23

2

Unused

AFE_STBY

2

0

AFE Standby (0 = Full Standby, 1 = Normal Operation,

2/3 = Reference Standby).

Digital Standby (0 = Full Standby, 1 = Normal Operation).

2

(23:3)

(7:0)

8

9

10

11

12

13

14

(16:15)

17

18

(23:19)

0

1

2

3

1

21

8

1

1

1

1

1

1

1

2

1

1

5

1

1

1

1

0

DIG_STBY

Unused

REFBLACK

BC_EN

TESTMODE

TESTMODE

PBLK_LEVEL

TRISTATEOUT

RETIMEOUT_BAR 0 = Retime Data Outputs, 1 = Do Not Retime Data Outputs.

GRAY_ENCODE

1 = Gray Encode ADC Outputs.

TESTMODE

This register should always be set to 0.

TESTMODE

This register should always be set to 0.

TESTMODE

This register should always be set to 1.

Unused

VCKM_DIVIDE

VCKM Input Clock Divider (0 = VCKM, 1 = VCKM/2).

H1BLKRETIME

Retimes the H1 HBLK to Internal Clock.

LM_INVERT

LM Inversion Control (1 = Invert Programmed LM).

TGOFD_INVERT

TG and OFD Inversion Control (1 = Invert Programmed TG

and ODF).

VDHD_INVERT

VD and HD Inversion Control (1 = Invert Programmed VD

and HD; Note that Internal VD/HD Are HI Active).

MASTER

Operating Mode (0 = Slave Mode, 1 = Master Mode).

Unused

SHDLOC

SHD Sample Location.

SHPLOC

SHP Sample Location.

DOUTPHASE

Data Output [9:0] and VCLK Phase Adjustment.

DOUT_DELAY

Data Output Clock Selection (0 = No Delay, 1 = ~4 ns, 2 = ~8 ns,

3 = ~12 ns).

VCLKMASK

VCLK Masking Control (1 = Mask).

VCLK_INVERT

1 = Invert VCLK.

DTEST

1 = Internal Digital Signal Test Mode.

Unused

H1POSLOC

H1 Positive Edge Location.

H1NEGLOC

H1 Negative Edge Location.

RSPOSLOC

RS Positive Edge Location.

RSNEGLOC

RS Negative Edge Location.

H1DRV

H1A/B/C/D Drive Strength (0 = OFF, 1 = 1.75 mA, 2 = 3.5 mA,

3 = 5.25 mA, 4 = 7 mA, 5 = 8.75 mA, 6 = 10.5 mA, 7 = 12.25 mA).

H2DRV

H2A/B Drive Strength (see H1DRV).

RSDRV

RS Drive Strength (see H1DRV).

Unused

Unused

3

0x80

1

0

0

0

0

0

0

0

0

1

Black Clamp Level.

1 = Black Clamp Enable.

This register should always be set to 0.

This register should always be set to 0.

0 = Blank to 0, 1 = Blank to Clamp Level (REFBLACK).

0 = Data Outputs are Driven, 1 = Data Outputs are Three-Stated.

4

0

0

0

0

4

1

0

5

(23:6)

(5:0)

(11:6)

(17:12)

(19:18)

1

18

6

6

6

2

0

5

0x00

0x24

0x00

0x00

20

21

22

23

(5:0)

(11:6)

(17:12)

(23:18)

(2:0)

1

1

1

1

6

6

6

6

3

0

1

0

–

0x00

0x20

0x00

0x10

4

6

7

(5:3)

(8:6)

(23:9)

(23:1)

3

3

15

23

4

4

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9937KCP | CCD Signal Processor with Precision Timing⑩ Generator |

| AD9937KCPRL | TVPS00RF-25-35PB W/ PC CONTACT |

| AD9942 | Dual-Channel, 14-Bit CCD Signal Processor with Precision Timing⑩ Core |

| AD9942BBCZ | Dual-Channel, 14-Bit CCD Signal Processor with Precision Timing⑩ Core |

| AD9942BBCZRL | Dual-Channel, 14-Bit CCD Signal Processor with Precision Timing⑩ Core |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9937BCPZ-24 | 制造商:Analog Devices 功能描述: |

| AD9937BCPZ-27 | 功能描述:IC CCD SIGNAL PROC/GEN 制造商:analog devices inc. 系列:* 零件狀態(tài):上次購買時間 標(biāo)準(zhǔn)包裝:1 |

| AD9937BCPZRL-24 | 制造商:Analog Devices 功能描述: |

| AD9937BCPZRL-27 | 功能描述:IC CCD SIGNAL PROC/GEN 制造商:analog devices inc. 系列:* 零件狀態(tài):上次購買時間 標(biāo)準(zhǔn)包裝:1 |

| AD9937KCP | 制造商:Analog Devices 功能描述:AFE Video 1ADC 10-Bit 3V 56-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。