- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375230 > AD1843JS (ANALOG DEVICES INC) CAP 3300PF 100V CERAMIC DISC Y5P PDF資料下載

參數(shù)資料

| 型號(hào): | AD1843JS |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | CAP 3300PF 100V CERAMIC DISC Y5P |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| 封裝: | PLASTIC, QFP-80 |

| 文件頁數(shù): | 51/64頁 |

| 文件大小: | 848K |

| 代理商: | AD1843JS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁當(dāng)前第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

AD1843

REV. 0

–51–

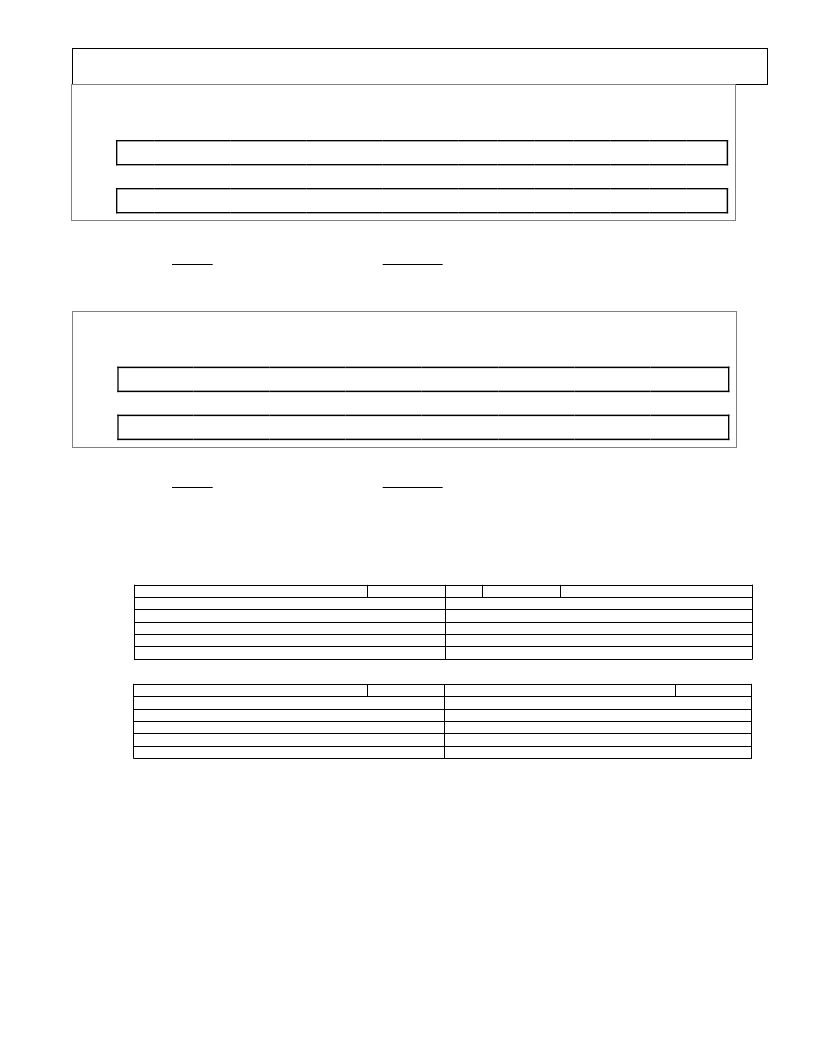

Address 30

Reserved for Future Expansion

Data 15

Data 14

Data 13

Data 12

Data 11

Data 10

Data 9

Data 8

res

res

res

res

res

res

res

res

Data 7

Data 6

Data 5

Data 4

Data 3

Data 2

Data 1

Data 0

res

res

res

res

res

res

res

res

res

Reserved for future expansion. To ensure future compatibility, write “0” to all reserved bits.

Initial default state after reset: 0000 0000 0000 0000 (0000 hex). Cleared to default and cannot be written to when:

the

RESET

pin is asserted LO; or when the

PWRDWN

pin is asserted LO.

Address 31

Reserved for Future Expansion

Data 15

Data 14

Data 13

Data 12

Data 11

Data 10

Data 9

Data 8

res

res

res

res

res

res

res

res

Data 7

Data 6

Data 5

Data 4

Data 3

Data 2

Data 1

Data 0

res

res

res

res

res

res

res

res

res

Reserved for future expansion. To ensure future compatibility, write “0” to all reserved bits.

Initial default state after reset: 0000 0000 0000 0000 (0000 hex). Cleared to default and cannot be written to when:

the

RESET

pin is asserted LO; or when the

PWRDWN

pin is asserted LO.

BIT AND REGISTER MAPS

A map of all TDM time slot bit assignments and Control Register contents is summarized for reference as follows in Figure 14

and Figure 15:

INPUT SLOT

0 OR 16

1 OR 17

2 OR 18

3 OR 19

4 OR 20

5 OR 21

DATA 15

RES

DATA 15

DATA 15

DATA 15

DATA 15

DATA 15

DATA 14

RES

DATA 14

DATA 14

DATA 14

DATA 14

DATA 14

DATA 13

RES

DATA 13

DATA 13

DATA 13

DATA 13

DATA 13

DATA 12

RES

DATA 12

DATA 12

DATA 12

DATA 12

DATA 12

DATA 11

RES

DATA 11

DATA 11

DATA 11

DATA 11

DATA 11

DATA 10

RES

DATA 10

DATA 10

DATA 10

DATA 10

DATA 10

DATA 9

DA2V

DATA 9

DATA 9

DATA 9

DATA 9

DATA 9

DATA 8

DA1V

DATA 8

DATA 8

DATA 8

DATA 8

DATA 8

DATA 7

R/W

DATA 7

DATA 7

DATA 7

DATA 7

DATA 7

DATA 6

RES

DATA 6

DATA 6

DATA 6

DATA 6

DATA 6

DATA 5

RES

DATA 5

DATA 5

DATA 5

DATA 5

DATA 5

DATA 4

IA4

DATA 4

DATA 4

DATA 4

DATA 4

DATA 4

DATA 3

IA3

DATA 3

DATA 3

DATA 3

DATA 3

DATA 3

DATA 2

IA2

DATA 2

DATA 2

DATA 2

DATA 2

DATA 2

DATA 1

IA1

DATA 1

DATA 1

DATA 1

DATA 1

DATA 1

DATA 0

IA0

DATA 0

DATA 0

DATA 0

DATA 0

DATA 0

OUTPUT SLOT

0 OR 16

1 OR 17

2 OR 18

3 OR 19

4 OR 20

5 OR 21

DATA 15

RES

DATA 15

DATA 15

DATA 15

RES

RES

DATA 14

RES

DATA 14

DATA 14

DATA 14

RES

RES

DATA 13

RES

DATA 13

DATA 13

DATA 13

RES

RES

DATA 12

RES

DATA 12

DATA 12

DATA 12

RES

RES

DATA 11

RES

DATA 11

DATA 11

DATA 11

RES

RES

DATA 10

RES

DATA 10

DATA 10

DATA 10

RES

RES

DATA 9

ADRV

DATA 9

DATA 9

DATA 9

RES

RES

DATA 8

ADLV

DATA 8

DATA 8

DATA 8

RES

RES

DATA 7

RES

DATA 7

DATA 7

DATA 7

RES

RES

DATA 6

RES

DATA 6

DATA 6

DATA 6

RES

RES

DATA 5

RES

DATA 5

DATA 5

DATA 5

RES

RES

DATA 4

RES

DATA 4

DATA 4

DATA 4

RES

RES

DATA 3

RES

DATA 3

DATA 3

DATA 3

RES

RES

DATA 2

RES

DATA 2

DATA 2

DATA 2

RES

RES

DATA 1

DA2RQ

DATA 1

DATA 1

DATA 1

RES

RES

DATA 0

DA1RQ

DATA 0

DATA 0

DATA 0

RES

RES

Figure 14. AD1843 TDM Time Slot Bit Assignment Map

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD1843JST | Serial-Port 16-Bit SoundComm Codec |

| AD1846JP | Low Cost Parallel-Port 16-Bit SoundPort Stereo Codec |

| AD1849KP | Serial-Port 16-Bit SoundPort Stereo Codec |

| AD1851 | 16-Bit, 16×Fs PCM Audio DACs(16位,單片PCM音頻D/A轉(zhuǎn)換器) |

| AD1892JR | Integrated Digital Receiver/Rate Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD1843JST | 制造商:AD 制造商全稱:Analog Devices 功能描述:Serial-Port 16-Bit SoundComm Codec |

| AD1845 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Parallel-Port 16-Bit SoundPort Stereo Codec |

| AD1845JP | 制造商:Analog Devices 功能描述:Audio Codec 2ADC / 2DAC 16-Bit 68-Pin PLCC 制造商:Rochester Electronics LLC 功能描述:16 BIT AUDIO CODEC - Bulk 制造商:Analog Devices 功能描述:IC CODEC 16-BIT AUDIO |

| AD1845JP-REEL | 制造商:Analog Devices 功能描述:Audio Codec 2ADC / 2DAC 16-Bit 68-Pin PLCC T/R |

| AD1845JPZ | 制造商:Analog Devices 功能描述:Audio Codec 2ADC / 2DAC 16-Bit 68-Pin PLCC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。