- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384004 > TLC320AD55C (Texas Instruments, Inc.) Sigma-Delta Analog Interface Circuit(Sigma-Delta 模擬接口) PDF資料下載

參數(shù)資料

| 型號(hào): | TLC320AD55C |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Sigma-Delta Analog Interface Circuit(Sigma-Delta 模擬接口) |

| 中文描述: | sigma - delta模擬接口電路(Σ-Δ模擬接口) |

| 文件頁(yè)數(shù): | 11/41頁(yè) |

| 文件大小: | 256K |

| 代理商: | TLC320AD55C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)

1–5

1.5

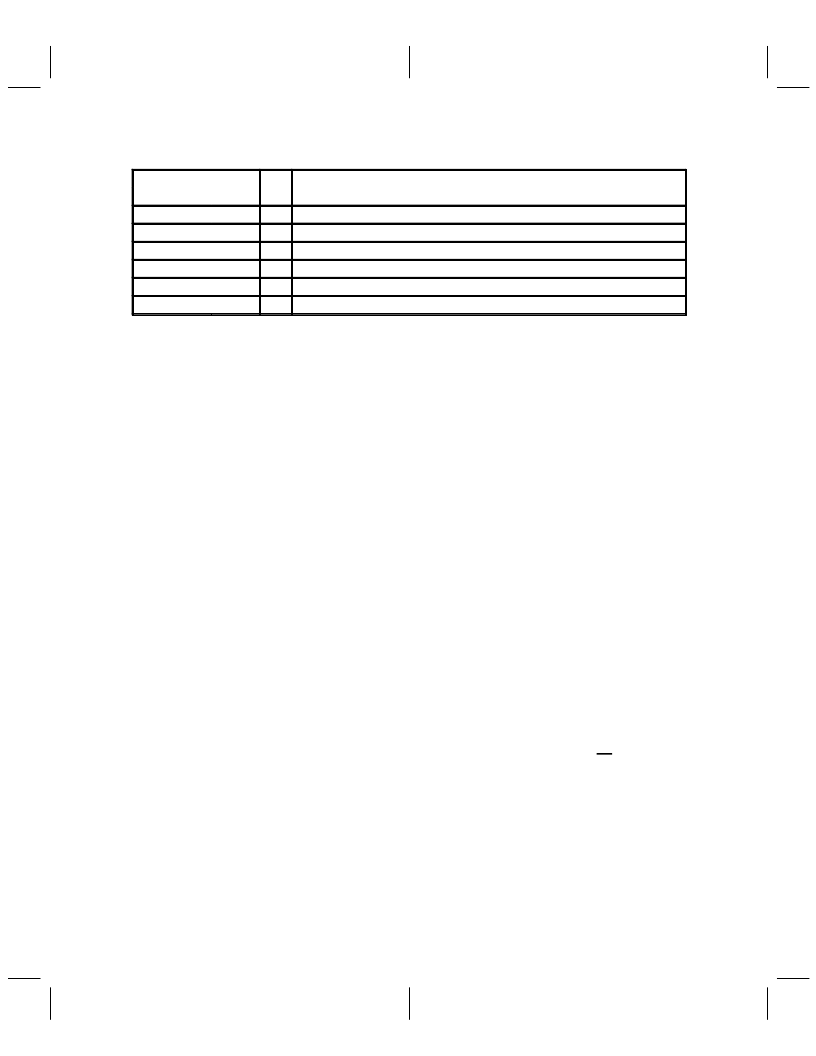

Terminal Functions (Continued)

TERMINALS

NAME

NO.

VA(SUB)

22

VD(SUB)

19

VDD(ADC)

24

VDD(DAC)

5

VSS(ADC)

21

VSS(DAC)

7

NOTE 1: All digital inputs and outputs are TTL compatible unless otherwise noted.

DESCRIPTION

I/O

I

Analog substrate. VA(SUB) must be grounded.

Digital substrate. VD(SUB) must be grounded.

Analog ADC path supply

I

I

I

Analog DAC path supply

I

Analog ADC path ground

I

Analog DAC path ground

1.6

Data Transfer Interval

Definitions and Terminology

The time during which data is transferred from DOUT and to DIN. The interval is

16 shift clocks and this data transfer is initiated by the falling edge of the frame-sync

signal.

Signal Data

The input signal and all of the converted representations through the ADC channel

and return through the DAC channel to the analog output. This is contrasted with

the purely digital software control data.

Primary

Communications

The digital data transfer interval. Since the device is synchronous, the signal data

words from the ADC channel and to the DAC channel occur simultaneously.

Secondary

Communications

The digital control and configuration data transfer interval into DIN and the register

read data cycle from DOUT. The data transfer interval occurs when requested by

hardware or software.

Frame Sync

The falling edge of the signal that initiates the data transfer interval. The primary

frame sync starts the primary communications, and the secondary frame sync

starts the secondary communications.

Frame Sync and

Sampling Period

The time between falling edges of successive primary frame-sync signals.

f

s

The sampling frequency that is the reciprocal of the sampling period.

Frame-Sync Interval

The time period occupied by 16 shift clocks. It goes high on the sixteenth rising

edge of SCLK after the falling edge of the frame sync.

ADC Channel

All signal processing circuits between the analog input and the digital conversion

results at DOUT.

DAC Channel

All signal processing circuits between the digital data word applied to DIN and the

differential output analog signal available at OUTP and OUTM.

Host

Any processing system that interfaces to DIN, DOUT, SCLK, or FS.

Dxx

A bit position in the primary data word (xx is the bit number).

DSxx

A bit position in the secondary data word (xx is the bit number).

d

The alpha character d is used to represent valid programmed or default data in the

control register format (see secondary serial communications) when discussing

other data bit portions of the register.

X

The alpha character X represents a don’t-care bit position within the control register

format.

FIR

Finite-duration impulse response.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLC320AD56(中文) | Sigma-Delta Analog Interface Circuit(Sigma-Delta 模擬接口) |

| TLC320AD56C | Sigma-Delta Analog Interface Circuit |

| tlc320ad56c | Sigma-Delta Analog Interface Circuit(Sigma-Delta 模擬接口電路) |

| TLC320AD57(中文) | Sigma-Delta Analog Interface Circuit(Sigma-Delta立體聲音頻ADC) |

| TLC320AD57C | Sigma-Delta Stereo Analog-to-Digital Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLC320AD56 | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:Sigma-Delta Analog Interface Circuit |

| TLC320AD56C | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:Sigma-Delta Analog Interface Circuit |

| TLC320AD56CFN | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TLC320AD56CPT | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TLC320AD57 | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:Sigma-Delta Stereo Analog-to-Digital Converter |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。