- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383876 > T8535 (Lineage Power) Quad Programmable Codec(四通道可編程編解碼器) PDF資料下載

參數(shù)資料

| 型號: | T8535 |

| 廠商: | Lineage Power |

| 元件分類: | Codec |

| 英文描述: | Quad Programmable Codec(四通道可編程編解碼器) |

| 中文描述: | 四可編程編解碼器(四通道可編程編解碼器) |

| 文件頁數(shù): | 47/54頁 |

| 文件大小: | 1872K |

| 代理商: | T8535 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁當(dāng)前第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

Lucent Technologies Inc.

47

Preliminary Data Sheet

July 2000

T8535/T8536 Quad Programmable Codec

Software Interface

(continued)

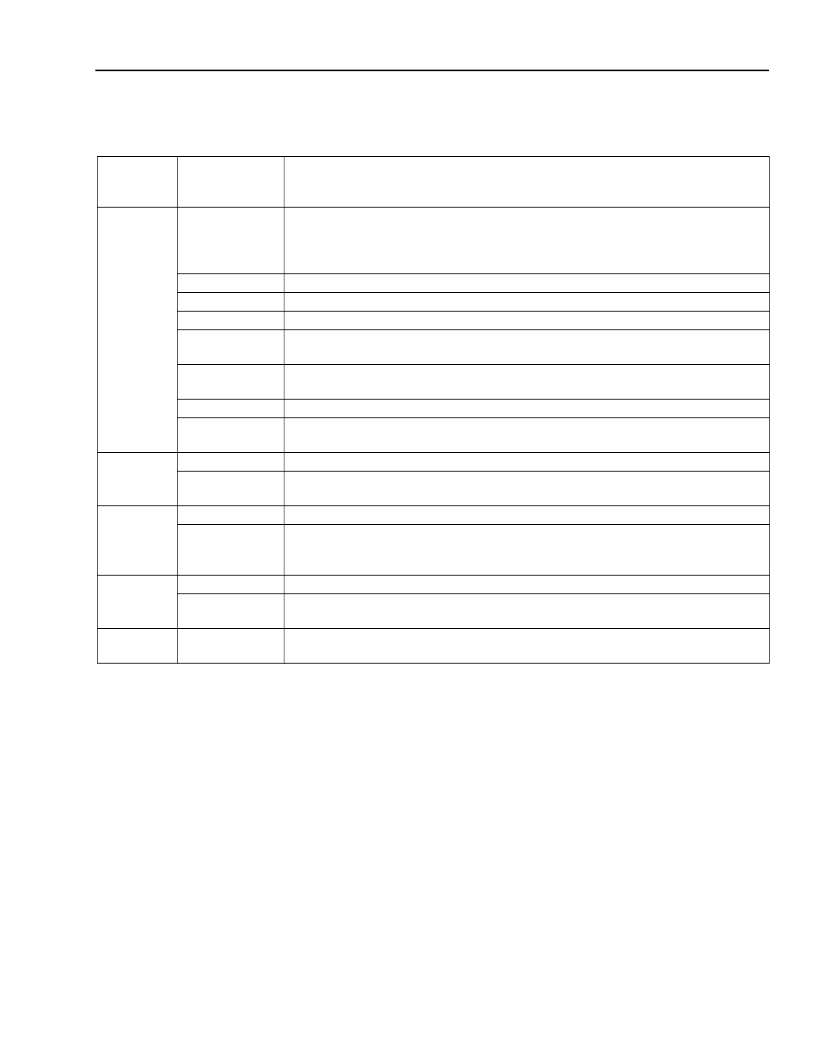

Table 21. Control Bit Definition

(continued)

Control

Name

(Address)

PCMCTRL1

(157)

Bit

Assignment(s)

Function

7

3-state transmit PCM interface. Defaults to zero. A one forces the PCM interface

into a high-impedance state during its assigned time-slot on the PCM bus. Plac-

ing the channel in standby mode also forces a high-impedance condition on the

transmit interface.

Transmit zeros instead of data. Defaults to zero (off).

Load as zero.

Place idle-channel code on receive path. Defaults to zero (off).

Loopback receive to transmit at PCM conversion interface (

digital loopback 1

).

Resets to zero.

Loopback transmit to receive at PCM conversion interface (

analog loopback 2

).

Resets to zero.

Reserved. Must be programmed to zero. Defaults to zero.

μ

-law or A-law. A one sets A-law mode, and a zero sets

μ

-law mode. Defaults to

zero (

μ

-law).

Load as zeros.

Controls the drivers for the corresponding SLIC latches. A one enables the lead

as an output. Defaults to 0x0C (bits 2 and 3 set, the rest cleared).

Load as zeros.

SLIC data latches. If the corresponding bit in the SLICTS address is set for an

output, the device will drive the corresponding bit according to the contents of this

address. Default is zero.

Not used, ignore on read.

Reports the actual state of the SLIC leads. Anything written to this address is

ignored, and within one PCM frame (125

μ

s), the data will be overwritten.

Test location for serial interface. This location has no internal use, but merely

latches write data for the purpose of testing the serial interface.

6

5

4

3

2

1

0

SLICTS

(158)

6—7

0—5

SLICWR

(159)

6—7

0—5

SLICRD

(160)

6—7

0—5

VERIFY

(162)

0—7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T8538A | Quad Programmable Codec(四通道可編程編解碼器) |

| T85HF10 | POWER RECTIFIER DIODES |

| T85HF100 | POWER RECTIFIER DIODES |

| T85HF120 | POWER RECTIFIER DIODES |

| T85HF20 | POWER RECTIFIER DIODES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T8535B | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8535B/T8536B Quad Programmable Codec |

| T8536B | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8535B/T8536B Quad Programmable Codec |

| T8538B | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8538B Quad Programmable Codec |

| T85471G | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

| T85471J | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。