- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄192300 > S29GL128N11FFIVH2 (SPANSION LLC) 16M X 16 FLASH 3V PROM, 110 ns, PBGA64 PDF資料下載

參數(shù)資料

| 型號(hào): | S29GL128N11FFIVH2 |

| 廠商: | SPANSION LLC |

| 元件分類: | PROM |

| 英文描述: | 16M X 16 FLASH 3V PROM, 110 ns, PBGA64 |

| 封裝: | 10 X 13 MM, 1 MM PITCH, LEAD FREE, FBGA-64 |

| 文件頁(yè)數(shù): | 27/74頁(yè) |

| 文件大小: | 1593K |

| 代理商: | S29GL128N11FFIVH2 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)

May 1, 2006 S29GL-N_01_A0

S29GL-N

31

Data

She e t

9.

Common Flash Memory Interface (CFI)

The Common Flash Interface (CFI) specification outlines device and host system software interrogation

handshake, which allows specific vendor-specified software algorithms to be used for entire families of

devices. Software support can then be device-independent, JEDEC ID-independent, and forward- and

backward-compatible for the specified flash device families. Flash vendors can standardize their existing

interfaces for long-term compatibility.

This device enters the CFI Query mode when the system writes the CFI Query command, 98h, to address

55h, any time the device is ready to read array data. The system can read CFI information at the addresses

given in Table 9.1 to Table 9.3 on page 32. To terminate reading CFI data, the system must write the reset

command.

The system can also write the CFI query command when the device is in the autoselect mode. The device

enters the CFI query mode, and the system can read CFI data at the addresses given in Table 9.1 to

Table 9.4 on page 33. The system must write the reset command to return the device to reading array data.

For further information, please refer to the CFI Specification and CFI Publication 100, available via the World

Wide Web at http://www.amd.com/flash/cfi. Alternatively, contact your sales representative for copies of

these documents.

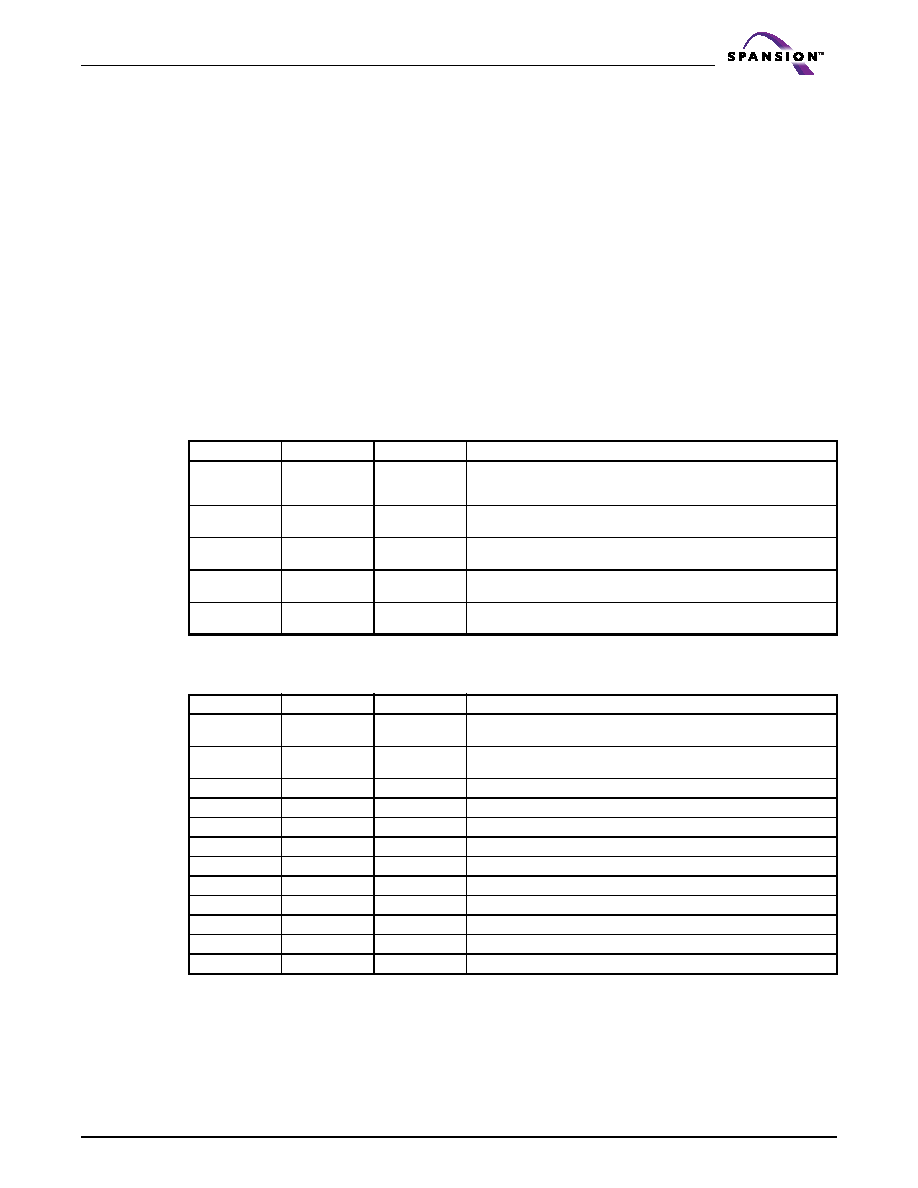

Table 9.1 CFI Query Identification String

Addresses (x16)

Addresses (x8)

Data

Description

10h

11h

12h

20h

22h

24h

0051h

0052h

0059h

Query Unique ASCII string “QRY”

13h

14h

26h

28h

0002h

0000h

Primary OEM Command Set

15h

16h

2Ah

2Ch

0040h

0000h

Address for Primary Extended Table

17h

18h

2Eh

30h

0000h

Alternate OEM Command Set (00h = none exists)

19h

1Ah

32h

34h

0000h

Address for Alternate OEM Extended Table (00h = none exists)

Table 9.2 System Interface String

Addresses (x16)

Addresses (x8)

Data

Description

1Bh

36h

0027h

VCC Min. (write/erase)

D7–D4: volt, D3–D0: 100 millivolt

1Ch

38h

0036h

VCC Max. (write/erase)

D7–D4: volt, D3–D0: 100 millivolt

1Dh

3Ah

0000h

VPP Min. voltage (00h = no VPP pin present)

1Eh

3Ch

0000h

VPP Max. voltage (00h = no VPP pin present)

1Fh

3Eh

0007h

Typical timeout per single byte/word write 2

N s

20h

40h

0007h

Typical timeout for Min. size buffer write 2

N

s (00h = not supported)

21h

42h

000Ah

Typical timeout per individual block erase 2N ms

22h

44h

0000h

Typical timeout for full chip erase 2

N ms (00h = not supported)

23h

46h

0003h

Max. timeout for byte/word write 2

N times typical

24h

48h

0005h

Max. timeout for buffer write 2N times typical

25h

4Ah

0004h

Max. timeout per individual block erase 2

N times typical

26h

4Ch

0000h

Max. timeout for full chip erase 2

N times typical (00h = not supported)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S29JL032J70TFI213 | 2M X 16 FLASH 3V PROM, 70 ns, PDSO48 |

| S29PL032J65BFI150 | 2M X 16 FLASH 3V PROM, 65 ns, PBGA56 |

| S29PL127J70BFI000 | 8M X 16 FLASH 3V PROM, 70 ns, PBGA80 |

| S29XS064R0PBHW010 | 4M X 16 FLASH 1.8V PROM, 80 ns, PBGA44 |

| S2C3R-1-12-H | 4000 MHz - 12000 MHz RF/MICROWAVE SGL POLE DOUBLE THROW SWITCH, 2 dB INSERTION LOSS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S29GL128N11FFVR10 | 制造商:Spansion 功能描述:FLASH PARALLEL 3.3V 128MBIT 16MX8/8MX16 110NS 56TSOP - Trays |

| S29GL128N11TAI010 | 制造商:Spansion 功能描述:SPZS29GL128N11TAI010 FLSH MEM EOL161008 |

| S29GL128N11TFA020 | 制造商:Spansion 功能描述: |

| S29GL128N11TFI010H | 制造商:Spansion 功能描述: |

| S29GL128N11TFI020 | 制造商:Spansion 功能描述: 制造商:Spansion 功能描述:Flash - NOR IC 制造商:Spansion 功能描述:NOR Flash, 8M x 16, 56 Pin, Plastic, TSSOP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。