- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄192300 > S29GL128N11FAIVH0 (SPANSION LLC) 16M X 16 FLASH 3V PROM, 110 ns, PBGA64 PDF資料下載

參數(shù)資料

| 型號(hào): | S29GL128N11FAIVH0 |

| 廠商: | SPANSION LLC |

| 元件分類: | PROM |

| 英文描述: | 16M X 16 FLASH 3V PROM, 110 ns, PBGA64 |

| 封裝: | 10 X 13 MM, 1 MM PITCH, FBGA-64 |

| 文件頁(yè)數(shù): | 37/74頁(yè) |

| 文件大小: | 1593K |

| 代理商: | S29GL128N11FAIVH0 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)當(dāng)前第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)

40

S29GL-N

S29GL-N_01_A0 May 1, 2006

Da ta

Sh e e t

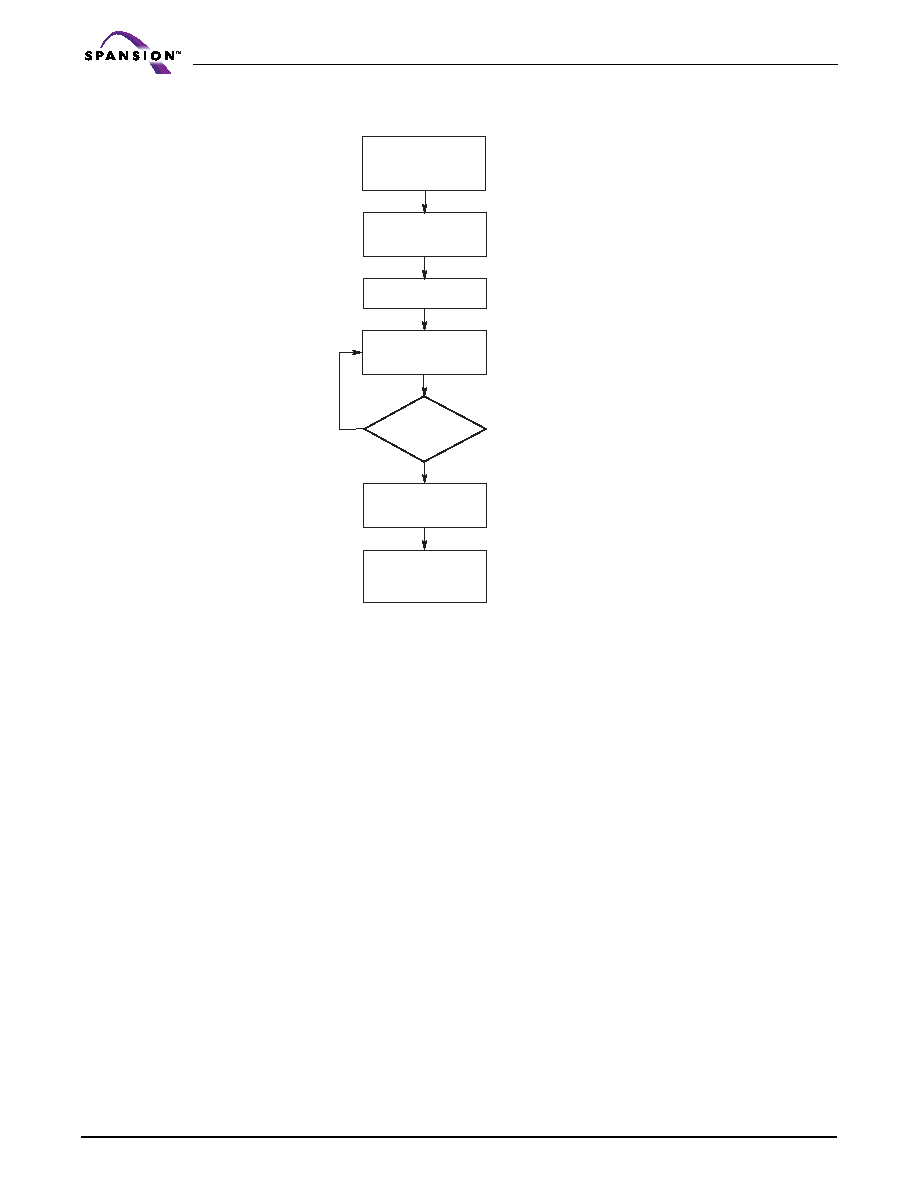

Figure 10.3 Program Suspend/Program Resume

10.7

Chip Erase Command Sequence

Chip erase is a six bus cycle operation. The chip erase command sequence is initiated by writing two unlock

cycles, followed by a set-up command. Two additional unlock write cycles are then followed by the chip erase

command, which in turn invokes the Embedded Erase algorithm. The device does not require the system to

preprogram prior to erase. The Embedded Erase algorithm automatically preprograms and verifies the entire

memory for an all zero data pattern prior to electrical erase. The system is not required to provide any

controls or timings during these operations. Table 11.1 on page 46 and Table 11.3 on page 48 show the

address and data requirements for the chip erase command sequence.

When the Embedded Erase algorithm is complete, the device returns to the read mode and addresses are no

longer latched. The system can determine the status of the erase operation by using DQ7, DQ6, or DQ2.

Refer to Write Operation Status on page 50 for information on these status bits.

Any commands written during the chip erase operation are ignored, including erase suspend commands.

However, note that a hardware reset immediately terminates the erase operation. If that occurs, the chip

erase command sequence should be reinitiated once the device has returned to reading array data, to ensure

data integrity.

Figure 10.4 on page 41 illustrates the algorithm for the erase operation. Note that the Secured Silicon

Sector, autoselect, and CFI functions are unavailable when an erase operation in is progress. Refer to

Erase and Program Operations on page 62 for parameters, and Figure 18.6 on page 64 for timing diagrams.

Program Operation

or Write-to-Buffer

Sequence in Progress

Write Program Suspend

Command Sequence

Command is also valid for

Erase-suspended-program

operations

Autoselect and SecSi Sector

read operations are also allowed

Data cannot be read from erase- or

program-suspended sectors

Write Program Resume

Command Sequence

Read data as

required

Done

reading?

No

Yes

Write address/data

XXXh/30h

Device reverts to

operation prior to

Program Suspend

Write address/data

XXXh/B0h

Wait 15

μs

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S29GL128N11FFIVH2 | 16M X 16 FLASH 3V PROM, 110 ns, PBGA64 |

| S29JL032J70TFI213 | 2M X 16 FLASH 3V PROM, 70 ns, PDSO48 |

| S29PL032J65BFI150 | 2M X 16 FLASH 3V PROM, 65 ns, PBGA56 |

| S29PL127J70BFI000 | 8M X 16 FLASH 3V PROM, 70 ns, PBGA80 |

| S29XS064R0PBHW010 | 4M X 16 FLASH 1.8V PROM, 80 ns, PBGA44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S29GL128N11FFA010 | 制造商:Spansion 功能描述: |

| S29GL128N11FFA013 | 制造商:Spansion 功能描述: |

| S29GL128N11FFI010 | 制造商:Spansion 功能描述:Flash - NOR IC |

| S29GL128N11FFI020 | 制造商:Spansion 功能描述: 制造商:Spansion 功能描述:Flash - NOR IC |

| S29GL128N11FFIIH0 | 制造商:Spansion 功能描述:NOR Flash Parallel 3V/3.3V 128Mbit 16M/8M x 8bit/16bit 110ns 64-Pin Fortified BGA Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。