- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369950 > PCI1520-EP Military Enhanced Plastic PC Card Controllers Data Manual PDF資料下載

參數(shù)資料

| 型號: | PCI1520-EP |

| 英文描述: | Military Enhanced Plastic PC Card Controllers Data Manual |

| 中文描述: | 軍事增強塑料PC卡控制器數(shù)據(jù)手冊 |

| 文件頁數(shù): | 57/125頁 |

| 文件大小: | 716K |

| 代理商: | PCI1520-EP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁當(dāng)前第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁

4

–

4

4.5

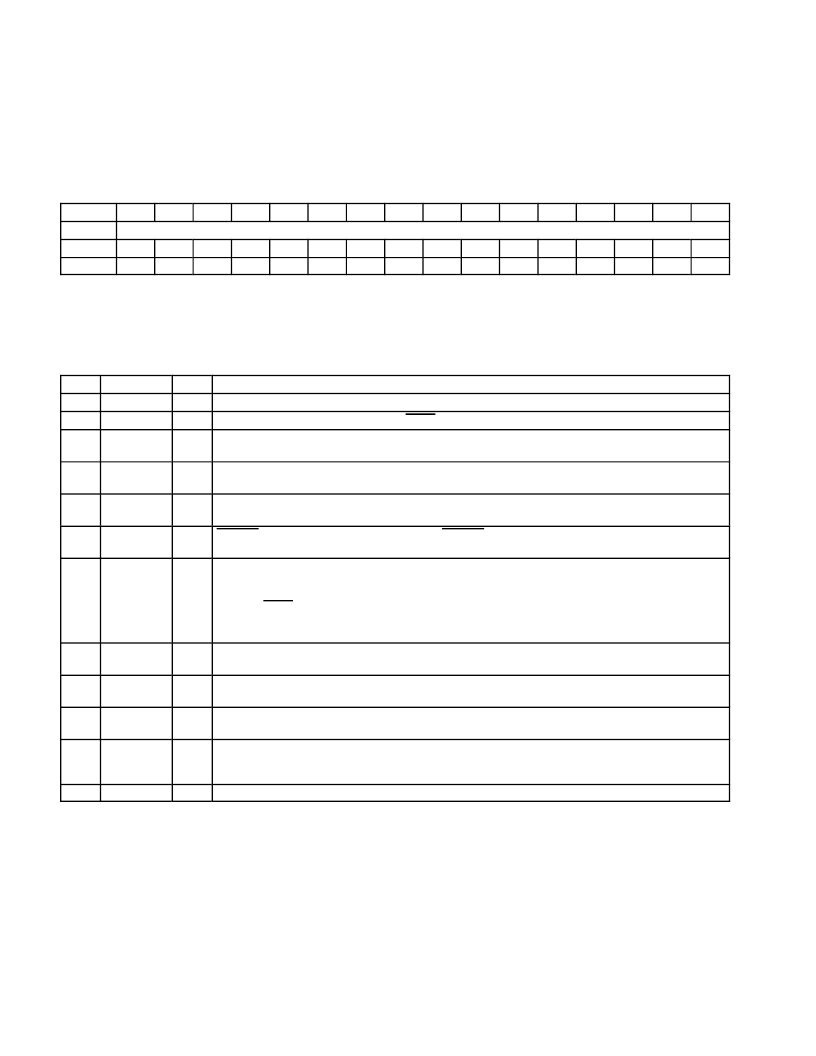

Status Register

The status register provides device information to the host system. Bits in this register can be read normally. A bit

in the status register is reset when a 1 is written to that bit location; a 0 written to a bit location has no effect. All bit

functions adhere to the definitions in the

PCI Local Bus Specification

. PCI bus status is shown through each function.

See Table 4

–

4 for a complete description of the register contents.

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Status

Type

RC

RC

RC

RC

RC

R

R

RC

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

1

0

0

0

0

1

0

0

0

0

Register:

Offset:

Type:

Default:

Status

06h (functions 0, 1)

Read-only, Read/Clear

0210h

Table 4

–

4. Status Register Description

BIT

SIGNAL

TYPE

FUNCTION

15

PAR_ERR

RC

Detected parity error. Bit 15 is set when a parity error is detected (either address or data).

14

SYS_ERR

RC

Signaled system error. Bit 14 is set when SERR is enabled and the PCI1520 signals a system error to the host.

13

MABORT

RC

Received master abort. Bit 13 is set when a cycle initiated by the PCI1520 on the PCI bus is terminated by a

master abort.

12

TABT_REC

RC

Received target abort. Bit 12 is set when a cycle initiated by the PCI1520 on the PCI bus is terminated by a target

abort.

11

TABT_SIG

RC

Signaled target abort. Bit 11 is set by the PCI1520 when it terminates a transaction on the PCI bus with a target

abort.

10

–

9

PCI_SPEED

R

DEVSEL timing. These bits encode the timing of DEVSEL and are hardwired 01b, indicating that the PCI1520

asserts PCI_SPEED at a medium speed on nonconfiguration cycle accesses.

8

DATAPAR

RC

Data parity error detected.

0 = The conditions for setting bit 8 have not been met.

1 = A data parity error occurred, and the following conditions were met:

a. PERR was asserted by any PCI device including the PCI1520.

b. The PCI1520 was the bus master during the data parity error.

c. The parity error response bit is set in the command register (PCI offset 04h, see Section 4.4).

7

FBB_CAP

R

Fast back-to-back capable. The PCI1520 cannot accept fast back-to-back transactions; therefore, bit 7 is

hardwired to 0.

6

UDF

R

User-definable feature support. The PCI1520 does not support the user-definable features; therefore, bit 6 is

hardwired to 0.

5

66MHZ

R

66-MHz capable. The PCI1520 operates at a maximum PCLK frequency of 33 MHz; therefore, bit 5 is hardwired

to 0.

4

CAPLIST

R

Capabilities list. Bit 4 returns 1 when read. This bit indicates that capabilities in addition to standard PCI

capabilities are implemented. The linked list of PCI power-management capabilities is implemented in this

function.

3

–

0

RSVD

R

Reserved. Bits 3

–

0 return 0s when read.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCI1620GHK | Controller Miscellaneous - Datasheet Reference |

| PCI1620PDV | Controller Miscellaneous - Datasheet Reference |

| PCI2050A | 32-Bit. 66MHz. 9-Master PCI-to-PCI Bridge |

| PCI2050GHK | BUS CONTROLLER |

| PCI2050PDV | BUS CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCI1520GHK | 功能描述:外圍驅(qū)動器與原件 - PCI PC CARD CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI1520I | 制造商:TI 制造商全稱:Texas Instruments 功能描述:PC CARD CONTROLLERS |

| PCI1520IGHK | 功能描述:外圍驅(qū)動器與原件 - PCI PC CARD CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI1520IGHKEP | 功能描述:外圍驅(qū)動器與原件 - PCI Mil Enhance PC Card Cntrlr Data Manual RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI1520IPDV | 功能描述:外圍驅(qū)動器與原件 - PCI PC CARD CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。