- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382382 > PCF85103C-2 (NXP Semiconductors N.V.) 256 x 8-bit CMOS EEPROM with I2C-bus interface PDF資料下載

參數(shù)資料

| 型號: | PCF85103C-2 |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | DRAM |

| 英文描述: | 256 x 8-bit CMOS EEPROM with I2C-bus interface |

| 中文描述: | 256 × 8位CMOS EEPROM,帶有I2C總線接口 |

| 文件頁數(shù): | 7/20頁 |

| 文件大?。?/td> | 346K |

| 代理商: | PCF85103C-2 |

Philips Semiconductors

PCF85103C-2

256

×

8-bit CMOS EEPROM with I

2

C-bus interface

Product data

Rev. 02 — 09 May 2002

7 of 20

9397 750 09646

Koninklijke Philips Electronics N.V. 2002. All rights reserved.

The master receiver must generate an acknowledge after the reception of each byte

that has been clocked out of the slave transmitter.

The device that acknowledges has to pull down the SDA line during the acknowledge

clock pulse in such a way that the SDA line is stable LOW during the HIGH period of

the acknowledge related clock pulse.

Set-up and hold times must be taken into account. A master receiver must signal an

end of data to the slave transmitter by not generating an acknowledge on the last byte

that has been clocked out of the slave. In this event, the transmitter must leave the

data line HIGH to enable the master generation of the STOP condition.

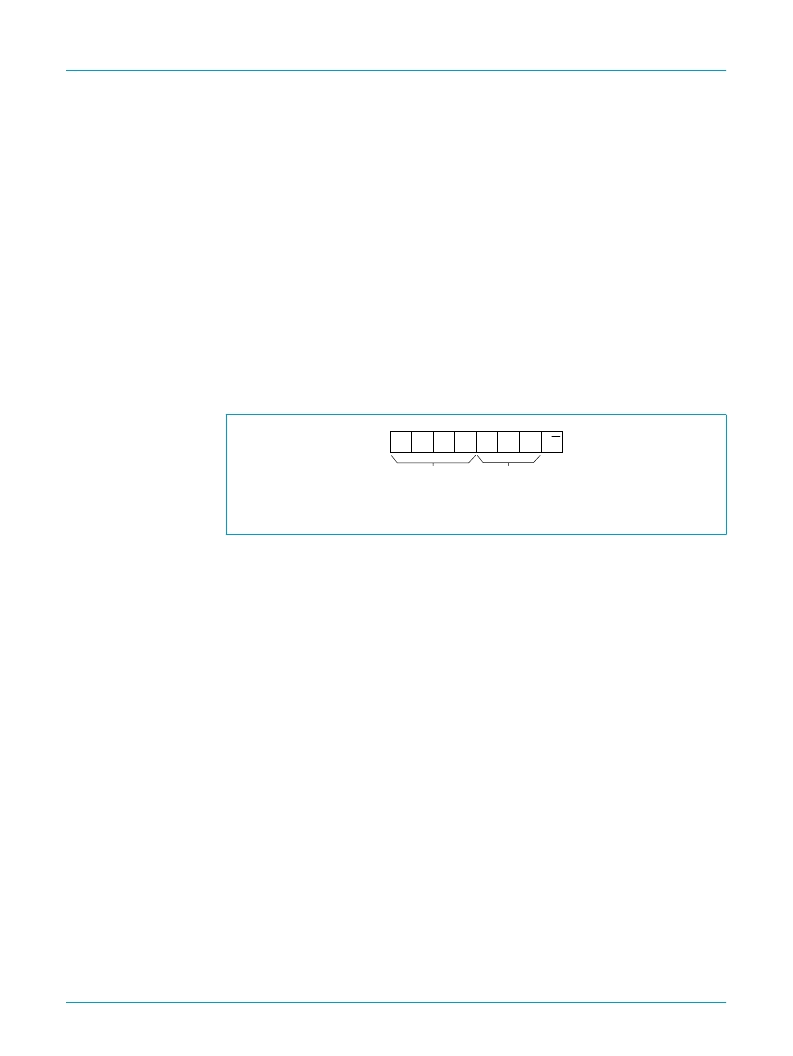

8.1.3

Device addressing

Following a START condition, the bus master must output the address of the slave it

is accessing. The address of the PCF85103C-2 is shown in

Figure 4

. To conserve

power, no internal pull-up resistors are incorporated on the hardware selectable pins

and they must be connected to either V

DD

or V

SS

.

The last bit of the slave address defines the operation to be performed. When set to

logic 1, a read operation is selected, while a logic 0 selects a write operation.

8.1.4

Write operations

Byte/word write:

For a write operation, the PCF85103C-2 requires a second

address field. This address field is a word address providing access to the 256 words

of memory. Upon receipt of the word address, the PCF85103C-2 responds with an

acknowledge and awaits the next eight bits of data, again responding with an

acknowledge. Word address is automatically incremented. The master can now

terminate the transfer by generating a STOP condition or transmit up to six more

bytes of data and then terminate by generating a STOP condition.

After this STOP condition, the E/W cycle starts and the bus is free for another

transmission. Its duration is 10 ms per byte.

During the E/W cycle the slave receiver does not send an acknowledge bit if

addressed via the I

2

C-bus.

Fig 4.

Slave address.

002aaa253

0

0

1

0

A2

A1

A0 R/W

FIXED

HARDWARE

SELECTABLE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCF8570 | 256 x 8-bit static low-voltage RAM with I2C-bus interface |

| PCF8575 | Remote 16-bit I/O expander for I2C-bus |

| PCF8576 | Universal LCD driver for low multiplex rates |

| PCF8576C | Universal LCD driver for low multiplex rates |

| PCF8576CH | Universal LCD driver for low multiplex rates |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCF85103C-2_04 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:256 x 8-bit CMOS EEPROM with I2C-bus interface |

| PCF85103C2D | 功能描述:電可擦除可編程只讀存儲器 256X8-BIT CMOS 電可擦除可編程只讀存儲器/I2C BUS RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| PCF85103C2N | 功能描述:電可擦除可編程只讀存儲器 256X8-BIT CMOS 電可擦除可編程只讀存儲器/I2C BUS RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| PCF85103C-2P | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:256 x 8-bit CMOS EEPROM with I2C-bus interface |

| PCF85103C-2P/00,11 | 功能描述:電可擦除可編程只讀存儲器 256X8-BIT CMOS RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。