- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄382352 > MTV112M (Electronic Theatre Controls, Inc.) 8051 Embedded CRT Monitor Controller Flash Version PDF資料下載

參數(shù)資料

| 型號(hào): | MTV112M |

| 廠(chǎng)商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 8051 Embedded CRT Monitor Controller Flash Version |

| 中文描述: | CRT顯示器8051嵌入式控制器Flash版本 |

| 文件頁(yè)數(shù): | 14/20頁(yè) |

| 文件大小: | 160K |

| 代理商: | MTV112M |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)

MYSON

TECHNOLOGY

MTV112M

(Rev 2.0)

Revision 2.0 - 14 - 2001/05/18

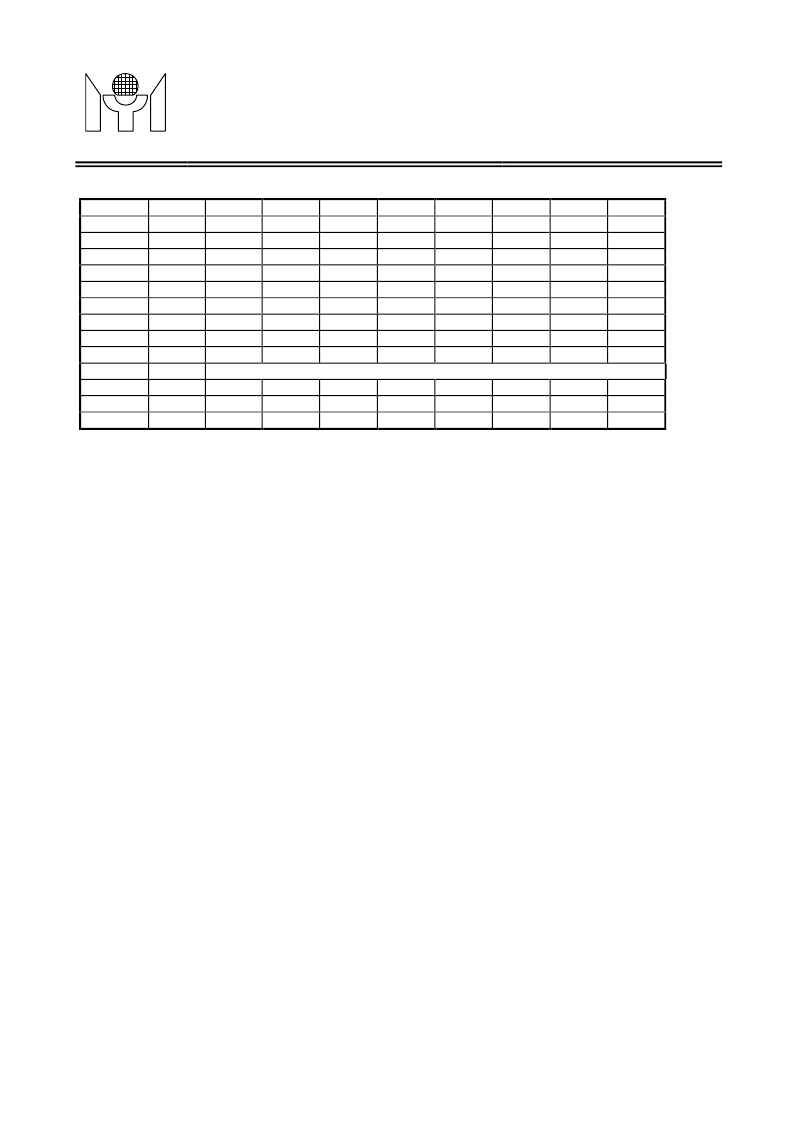

Reg name

MCTR

MSTUS

MCTR

MBUF

INTFLG

INTEN

FIFO

SLVCTR

SLVSTUS

SLVSTUS

91h (w)

RCBUF

TXBUF

SLVADR

addr

00h (w)

00h (r)

01h (w)

10h (r/w) MBUF7

50h (r/w) HPRchg VPRchg HPLchg VPLchg

60h (w)

EHPR

EVPR

70h (w)

FIFO7

FIFO6

90h (w)

ENSLV

SLVsel

91h (r)

WADR

SLVS

bit7

LS1

X

X

bit6

LS0

bit5

LDFIFO

DDC2

X

MBUF5

bit4

M256

BERR

X

MBUF4

bit3

M128

HFREQ

X

MBUF3

HFchg

EHF

FIFO3

ETXBI

TXBI

bit2

ACK

FIFOH

X

MBUF2

VFchg

EVF

FIFO2

ENSCL

RWB

bit1

P

FIFOL

MCLK1

MBUF1

FIFOI

EFIFO

FIFO1

X

ACKIN

bit0

S

BUSY

MCLK0

MBUF0

MI

EMI

FIFO0

X

X

SCLERR

X

MBUF6

EHPL

FIFO5

ERCBI

RCBI

EVPL

FIFO4

ESLVMI

SLVMI

Write to clear SLVMI

RCbuf4

TXbuf4

92h (r)

92h (w)

93h (w) SLVadr7 SLVadr6 SLVadr5 SLVadr4 SLVadr3 SLVadr2 SLVadr1

RCbuf7

TXbuf7

RCbuf6

TXbuf6

RCbuf5

TXbuf5

RCbuf3

TXbuf3

RCbuf2

TXbuf2

RCbuf1

TXbuf1

RCbuf0

TXbuf0

X

MCTR

(w) :

Master IIC interface control register.

LS1, LS0

= 11

= 10

= 01

= 00

LDFIFO

= 1

M256

= 1

M128

= 1

ACK

= 1

= 0

S, P

=

↑

, 0

= X,

↑

= 1, X

= X, 0

MCLK1 : MCLK0 : Master IIC speed select,

= 0

= 1

= 2

= 3

→

FIFOL is the status in which FIFO depth < 5.

→

FIFOL is the status in which FIFO depth < 4.

→

FIFOL is the status in which FIFO depth < 3.

→

FIFOL is the status in which FIFO depth < 2.

→

FIFO will be written while S/W reads MBUF.

→

Disables host writing EEPROM when address is over 256.

→

Disables host writing EEPROM when address is over 128.

→

In receiving mode, no acknowledgment is given by MTV112M.

→

In receiving mode, ACK is returned by MTV112M.

→

Start condition when Master IIC is not transferring.

→

Stop condition when Master IIC is not transferring.

→

Will resume transfer after a read/write MBUF operation.

→

Forces HSCL low and occupies the IIC bus.

→

50KHz for 8MHz X’tal, 75KHz for 12MHz X’tal.

→

100KHz for 8MHz X’tal, 150KHz for 12MHz X’tal.

→

200KHz for 8MHz X’tal, 300KHz for 12MHz X’tal .

→

400KHz for 8MHz X’tal, 600KHz for 12MHz X’tal.

* MTV112M uses a 100KHz clock to sample the S/P bit; any pulse should sustain at least 20us.

* A write/read MBUF operation can be recognized only after 10us of the MI flag's rising edge.

MSTUS

(r) :

Master IIC interface status register.

SCLERR

= 1

→

The ISCL pin has been pulled low by other devices during the transfer,

cleared when S=0.

→

DDC2B is active.

→

MTV112M remains in DDC1 mode.

→

IIC bus error, no ACK received from the slave, updated each time the

slave sends ACK on the ISDA pin.

→

MTV112M has detected a higher than 200Hz clock on the VSYNC pin.

→

FIFO high indicated.

→

FIFO low indicated.

→

Host drives the HSCL pin to low.

* While writing FIFO, the FIFOH/FIFOL flag will reflect the FIFO condition after 30us.

DDC2

= 1

= 0

= 1

BERR

HFREQ

FIFOH

FIFOL

BUSY

= 1

= 1

= 1

= 1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MTV118 | On-Screen-Display for LCD Monitor |

| MTV121 | Super On-Screen-Display for LCD Monitor |

| MUA08A | 265mW at 3.3V Supply Audio Power Amplifier with Shutdown Mode |

| MUB08A | 1W, Bypass-Capacitor-less Audio Amplifier with Internal Selectable Gain |

| MUBW10-06A7 | Converter - Brake - Inverter Module |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MTV1-12PAL39 | 制造商:ITT Interconnect Solutions 功能描述:MTV1-12PAL39 - Bulk |

| MTV1-12PCL1-1 | 制造商:ITT Interconnect Solutions 功能描述:MTV1-12PCL1-1 / 097432-0074 / Micro |

| MTV1-12PH001-04 | 制造商:ITT Interconnect Solutions 功能描述:Cable Assembly Pre-Wired Pigtail 0.457m 26AWG 12 POS Micro Strip PIN Crimp |

| MTV1-12PH002-01 | 制造商:ITT Interconnect Solutions 功能描述:MTV1-12PH002-01 - Bulk |

| MTV1-12PH003-01 | 制造商:ITT Interconnect Solutions 功能描述:MTV1-12PH003-01 - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。