- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384756 > MT49H32M9CFM-xx (Micron Technology, Inc.) 288Mb SIO REDUCED LATENCY(RLDRAM II) PDF資料下載

參數(shù)資料

| 型號(hào): | MT49H32M9CFM-xx |

| 廠商: | Micron Technology, Inc. |

| 英文描述: | 288Mb SIO REDUCED LATENCY(RLDRAM II) |

| 中文描述: | 288Mb二氧化硅約化延遲(延遲DRAM二) |

| 文件頁(yè)數(shù): | 9/44頁(yè) |

| 文件大小: | 1117K |

| 代理商: | MT49H32M9CFM-XX |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)

16 MEG x 18, 32 MEG x 9

2.5V V

EXT

, 1.8V V

DD

, HSTL, SIO, RLDRAM II

pdf: 09005aef80a41b59/zip: 09005aef811ba111

MT49H8M18C_2.fm - Rev. F 11/04 EN

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2004 Micron Technology, Inc. All rights reserved.

9

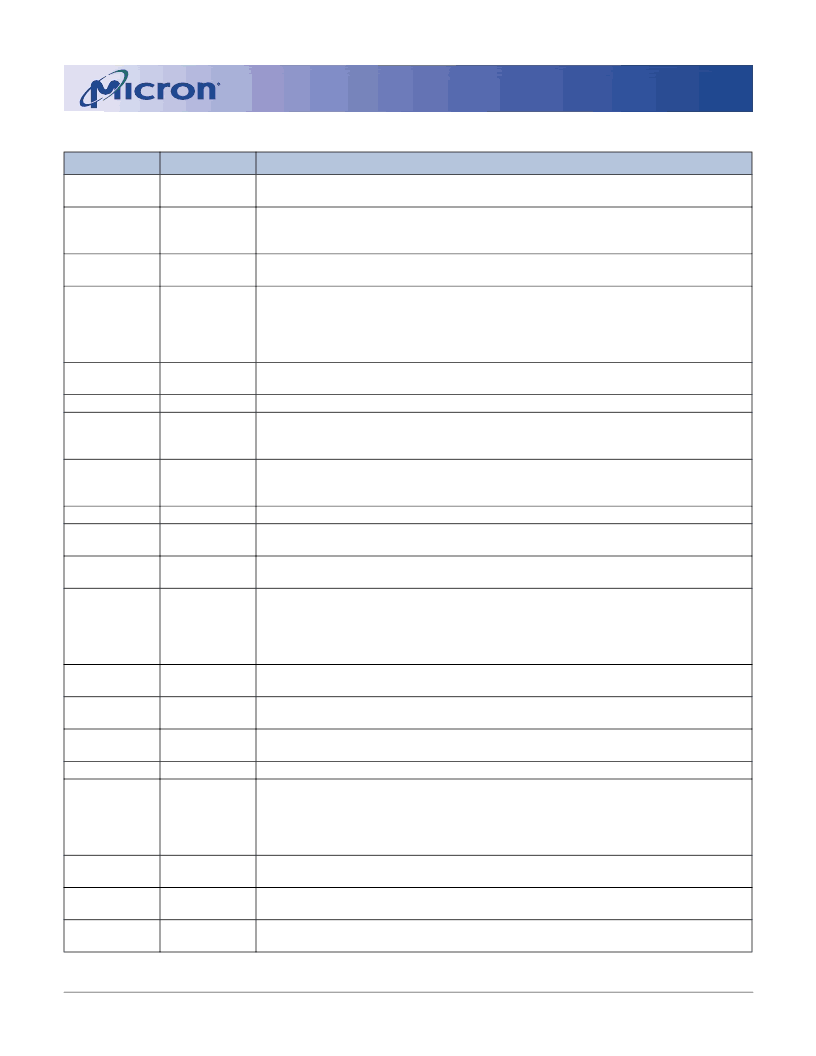

Table 2:

Ball Descriptions

SYMBOL

CK, CK#

TYPE

Input

DESCRIPTION

Input Clock: CK and CK# are differential clock inputs. Addresses and commands are

latched on the rising edge of CK. CK# is ideally 180 degrees out of phase with CK.

Chip Select: CS# enables the command decoder when LOW and disables it when HIGH.

When the command decoder is disabled, new commands are ignored, but internal

operations continue.

Command Inputs: Sampled at the positive edge of CK, WE#, and REF# define (together

with CS#) the command to be executed.

Address Inputs: A[0:20] define the row and column addresses for READ and WRITE

operations. During a MODE REGISTER SET, the address inputs define the register

settings. They are sampled at the rising edge of CK. In the x18 configuration, A[20] is

reserved for address expansion. These expansion addresses can be treated as address

inputs, but they do not affect the operation of the device.

Reserved for future use. This signal is internally connected and can be treated as an

address input.

Reserved for future use. This signal is not connected and may be connected to ground.

Input Data Clock: DKx and DKx# are the differential input data clocks. All input data is

referenced to both edges of DK. DK# is ideally 180 degrees out of phase with DK. D0–

D17 are referenced to DK0 and DK0#.

Input Data Mask: The DM signal is the input mask signal for WRITE data. Input data is

masked when DM is sampled HIGH, along with the WRITE input data. DM is sampled on

both edges of DK.

Bank Address Inputs: Select to which internal bank a command is being applied.

Data Input: The D signals form the 18-bit input data bus. During WRITE commands, the

data is referenced to both edges of DK.

Data Output: The Q signals form the 18-bit output data bus. During READ commands,

the data is referenced to both edges of QK.

Output Data Clocks: QKx and QKx# are opposite polarity, output data clocks. During

READs, they are free running and edge-aligned with data output from the RLDRAM.

QKx# is ideally 180 degrees out of phase with QKx. QK0 and QK0# are aligned with Q0–

Q8 and QK1 and QK1# are aligned with Q9–Q17. Consult the RLDRAM II Design Guide

for more details.

Data Valid: The QVLD indicates valid output data. QVLD is edge-aligned with QKx and

QKx#.

IEEE 1149.1 Test Inputs: These balls may be left as No Connects if the JTAG function is

not used in the circuit

IEEE 1149.1 Clock Input: This ball must be tied to V

SS

if the JTAG function is not used in

the circuit.

IEEE 1149.1 Test Output: JTAG output.

External Impedance [25

–60

]: This signal is used to tune the device outputs to the

system data bus impedance. Q output impedance is set to 0.2 x RQ, where RQ is a

resistor from this signal to ground. Connecting ZQ to GND invokes the minimum

impedance mode. Connecting ZQ to V

DD

invokes the maximum impedance mode. Refer

to Figure 10 on page 16 to activate this function.

Input Reference Voltage: Nominally V

DD

Q/2. Provides a reference voltage for the input

buffers.

Power Supply: 2.5V nominal. See Table 19, DC Electrical Characteristics and Operating

Conditions, on page 41 for range.

Power Supply: 1.8V nominal. See Table 19, DC Electrical Characteristics and Operating

Conditions, on page 41 for range.

CS#

Input

WE#, REF#

Input

A[0:20]

Input

A21

–

A22

–

DKx, DKx#

Input

DM

Input

BA[0:2]

D0–D17

Input

Input

Q0–Q17

Output

QKx, QKx#

Output

QVLD

Output

TMS

TDI

TCK

Input

Input

TDO

ZQ

Output

Input/Output

V

REF

Input

V

EXT

Supply

V

DD

Supply

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT4C1004J | 4 Meg x 1 FPM DRAM(4 M x 1快速頁(yè)面模式動(dòng)態(tài)RAM) |

| MT4C4001STG-6 | standard or self refresh |

| MT4C4001STG-7 | standard or self refresh |

| MT4C4001STG-8 | standard or self refresh |

| MT4C4001JDJ-6 | standard or self refresh |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT49H32M9CHU-25 | 制造商:Micron Technology Inc 功能描述:DRAM CHIP RLDRAM 288MBIT 1.8V 144FBGA - Trays |

| MT49H32M9CHU-33 | 制造商:Micron Technology Inc 功能描述:32MX9 RLDRAM PLASTIC FBGA 1.8V SEPARATE I/O 8 BANKS 1.8V I/O - Trays |

| MT49H32M9CHU-5 | 制造商:Micron Technology Inc 功能描述:32MX9 RLDRAM PLASTIC FBGA 1.8V SEPARATE I/O 8 BANKS 1.8V I/O - Trays |

| MT49H32M9FM-25 | 制造商:Micron Technology Inc 功能描述: |

| MT49H32M9FM-25 TR | 功能描述:IC RLDRAM 288MBIT 400MHZ 144FBGA RoHS:是 類(lèi)別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 產(chǎn)品變化通告:Product Discontinuation 05/Nov/2008 標(biāo)準(zhǔn)包裝:84 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類(lèi)型:SRAM - 同步 ZBT 存儲(chǔ)容量:4.5M(128K x 36) 速度:75ns 接口:并聯(lián) 電源電壓:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 封裝/外殼:119-BGA 供應(yīng)商設(shè)備封裝:119-PBGA(14x22) 包裝:托盤(pán) 其它名稱:71V3557SA75BGI |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。